Altera Stratix V Avalon-ST User Manual

Page 19

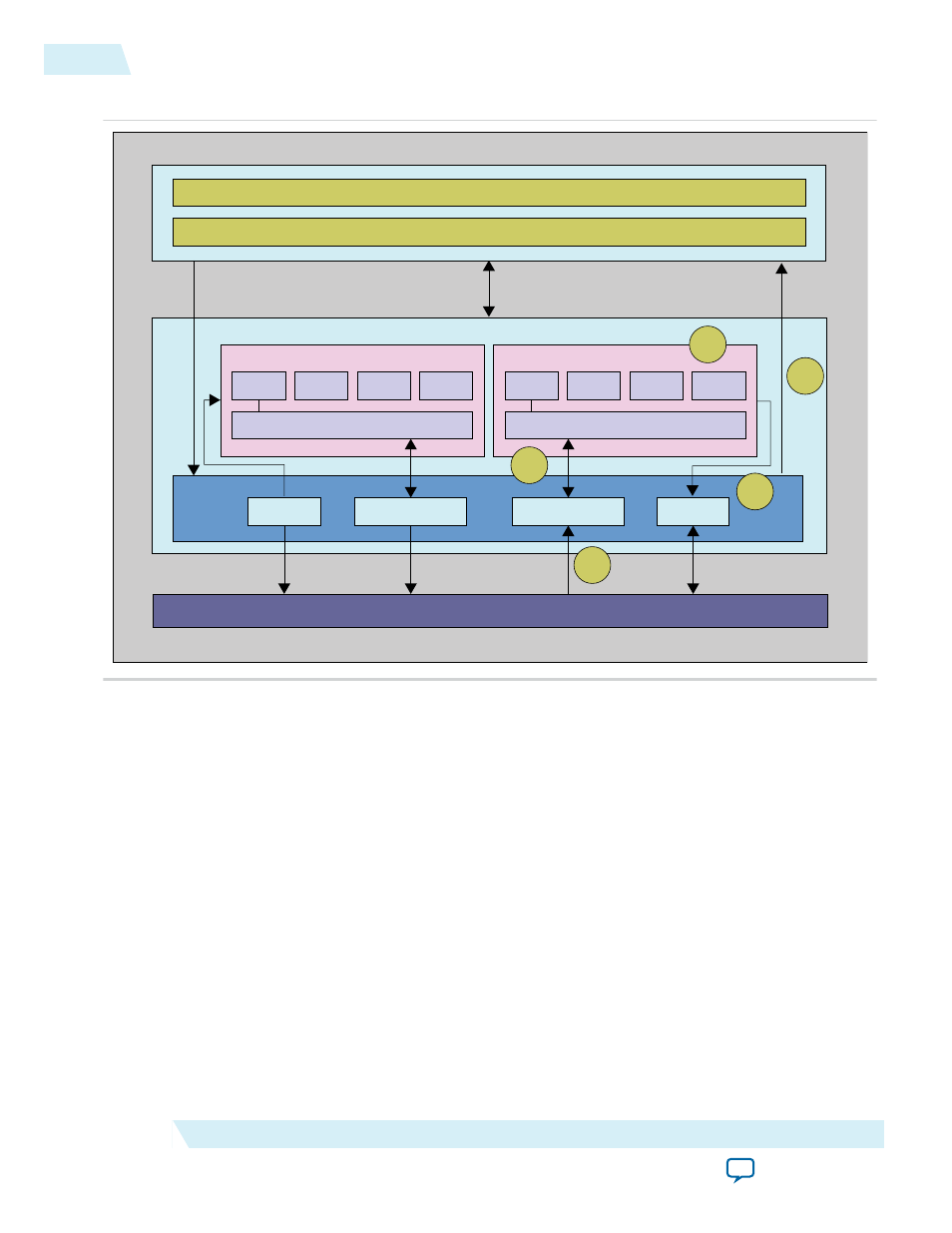

Figure 2-5: Steps To Perform a Write DMA

sriov_top_dma_gen3_x8_256.qsys

Stratix V Hard IP for PCI Express

SR-IOV Bridge

Rd_DC0

Rd_DC1

Rd_DC2

Rd_DC3

Read DMA Router

APPs - sriov_dma_app_g3x8_256b.qsys

rddc_ctl - rddc_ctl_256b.qsys

wrdc_ctl - wrdc_ctl_256b.qsys

Wr_DC0

Wr_DC1

Wr_DC2

Wr_DC3

Write DMA Router

User Application Logic (On-Chip Memories)

DMA Write

TX Slave

RX Master

DMA Read

1

3

5

4

2

The Write DMA operation includes the following steps:

1. The Descriptor Controller sends write descriptor instruction to initiate a DMA write.

2. The DMA Write reads data from the Application Layer memory.

3. Descriptor Controller transmits a Memory Write TLP to the host.

4. The DMA Write reports status for each descriptor to the Descriptor Controller.

5. When all descriptors are complete, the Descriptor Controller writes the ID of the last completed

descriptor to the

EPLAST

bit of the descriptor table.

Compiling the Example Design with the Quartus II Software

Complete the following steps to create and compile a Quartus II project.

1. In a terminal window, change to your working directory.

2. Copy the files from

<install_dir>/ ip/altera/altera_pcie/altera_pcie_sriov/hw_devkit/

directory to your

working directory.

2-8

Compiling the Example Design with the Quartus II Software

UG-01097_sriov

2014.12.15

Altera Corporation

Getting Started with the SR-IOV DMA Example Design