Interrupt line and interrupt pin register – Altera Stratix V Avalon-ST User Manual

Page 78

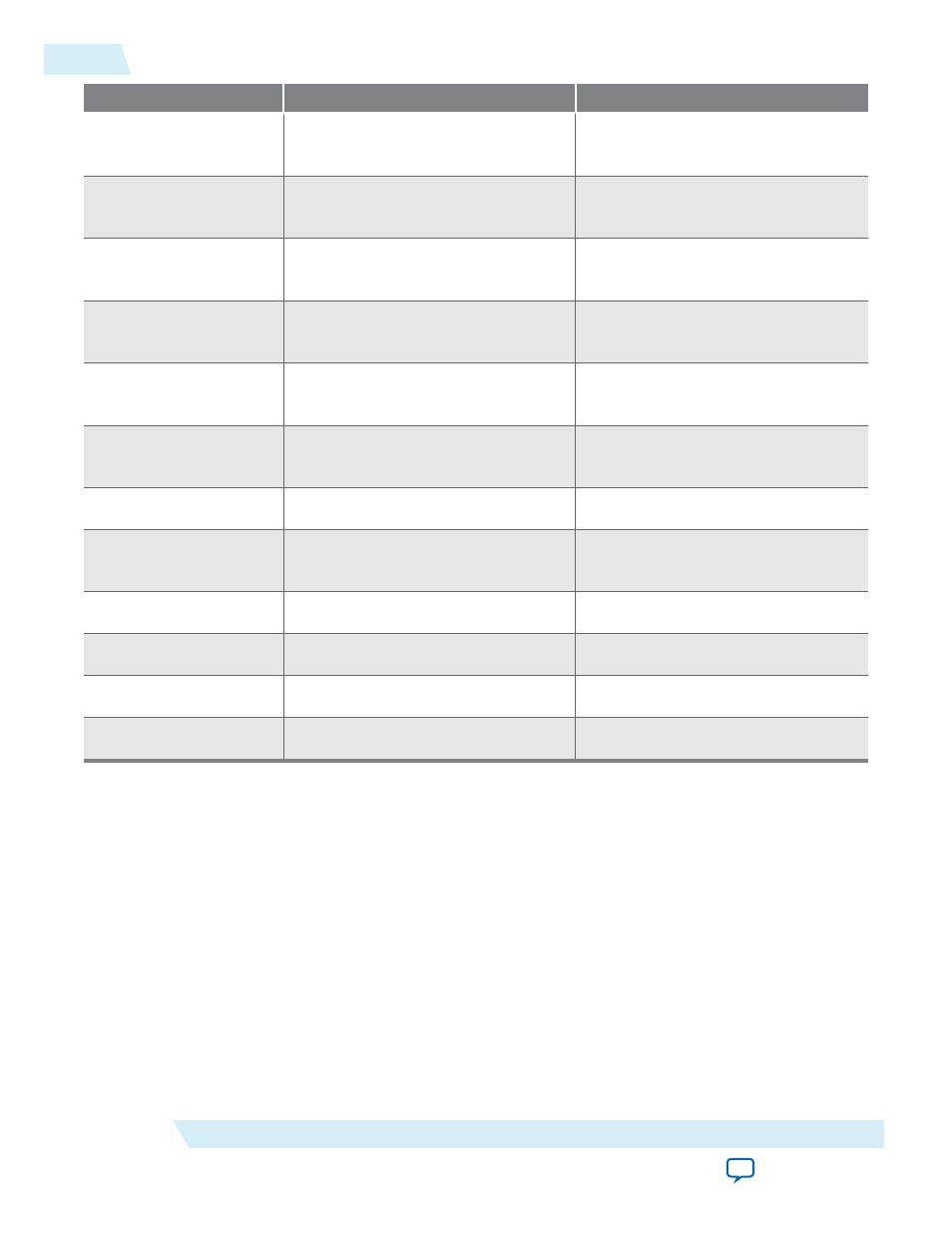

Byte Address

0x010

Base Address 0

Base Address Registers (Offset 10h -

24h)

0x014

Base Address 1

Base Address Registers (Offset 10h -

24h)

0x018

Base Address 2

Base Address Registers (Offset 10h -

24h)

0x01C

Base Address 3

Base Address Registers (Offset 10h -

24h)

0x020

Base Address 4

Base Address Registers (Offset 10h -

24h)

0x024

Base Address 5

Base Address Registers (Offset 10h -

24h)

0x028

Reserved

0x02C

Subsystem Device ID Subsystem Vendor

ID

Type 0 Configuration Space Header

0x030

Reserved

0x034

Capabilities PTR

Type 0 Configuration Space Header

0x038

Reserved

Type 0 Configuration Space Header

0x03C

0x00 Interrupt Pin Interrupt Line

Type 0 Configuration Space Header

PCI and PCI Express Configuration Space Register Content

For comprehensive information about these registers, refer to Chapter 7 of the PCI Express Base Specifica‐

tion Revision 3.0.

Related Information

Interrupt Line and Interrupt Pin Register

These registers are used only when you configure the Physical Function (PF) to support PCI legacy

interrupts. The following sequence of events implements a legacy interrupt:

5-4

PCI and PCI Express Configuration Space Register Content

UG-01097_sriov

2014.12.15

Altera Corporation

Registers