Altera Stratix V Avalon-ST User Manual

Page 132

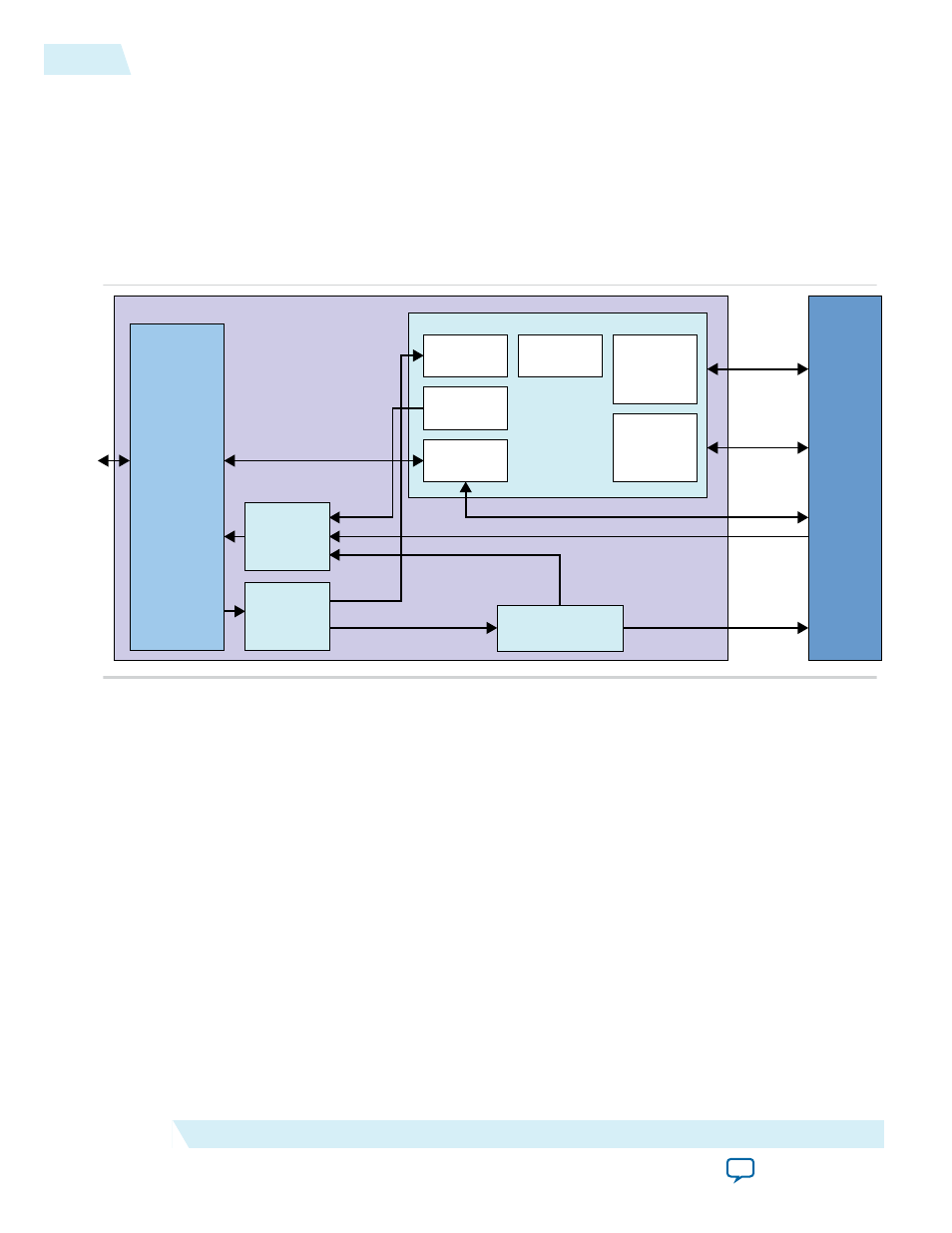

The SR-IOV processes memory requests, Completions and messages received from the link. It passes

them to the Application Layer unmodified, using the Avalon-ST RX interface. The SR-IOV Bridge does

not maintain any state for requests outstanding on the Master or Target sides. The RX interface delivers

Completion TLPs to the Application Layer in the same order as received from the link. It does not match

Completion TLPs with the outstanding requests from the Application Layer.

The following figure illustrates the SR-IOV Bridge logic and its interfaces to the Stratix V Hard IP for PCI

Express and Application Layer.

Figure 9-4: Block Diagram of the Stratix V Hard IP for PCI Express IP with the SR-IOV Bridge

Request

Processing

Completion

Generation

LMI Interface

Block

Error Message

Generation

PF

Registers

VF

Registers

Avalon-ST TX

Multiplexer

Avalon-ST RX

Demultiplexer

BAR Check and UR

Completion Generation

Stratix V

PCI Express

Hard IP Block

PIPE

Interface

LMI

Avalon-ST

TX Interface

Avalon-ST

RX Interface

Stratix V PCI Express SR-IOV Bridge

User

Application

Configuration Block

Control/Status

Interface

Interrupt

Interface

Local

Management

Interface

Avalon-ST

TX Interface

Avalon-ST

RX Interface

UR Completion

Configuration Completion,

Interrupts, and Error Messages

Configuration

Requests

SR-IOV Bridge Logic Details

Soft logic in the SR-IOV Bridge decodes Configuration Space transactions on Avalon-ST interface via

Configuration Bypass mode and forwards them to the internal Configuration Block. The Configuration

Block implements the following logic:

• Processes incoming Configuration Space TLPs and generates Completions

• Includes Configuration Space registers of two Physical Functions and 128 Virtual Functions.

• Generates MSI, MSI-X, and Legacy Interrupts (

INTx Assert and Deassert

)

• Generates error messages for AER

• Multiplexes the following data sources to on the Avalon-ST TX interface:

• Master-side requests and Target-side Completions generated by the Application Layer

• UR Completions from the BAR Check block for Memoroy Read Requests

• Transmits Memory Read and Memory Write received on TX Avalon-ST interface from the Applica‐

tion Layer. The core forwards these requests to the host as is, without any checking for errors. Applica‐

tion Layer logic must make sure the transmitted memory requests satisfy all PCI Express requirements.

9-8

Stratix V Hard IP for PCI Express with Single-Root I/O Virtualization (SR-IOV)

UG-01097_sriov

2014.12.15

Altera Corporation

IP Core Architecture