Altera Stratix V Avalon-ST User Manual

Page 91

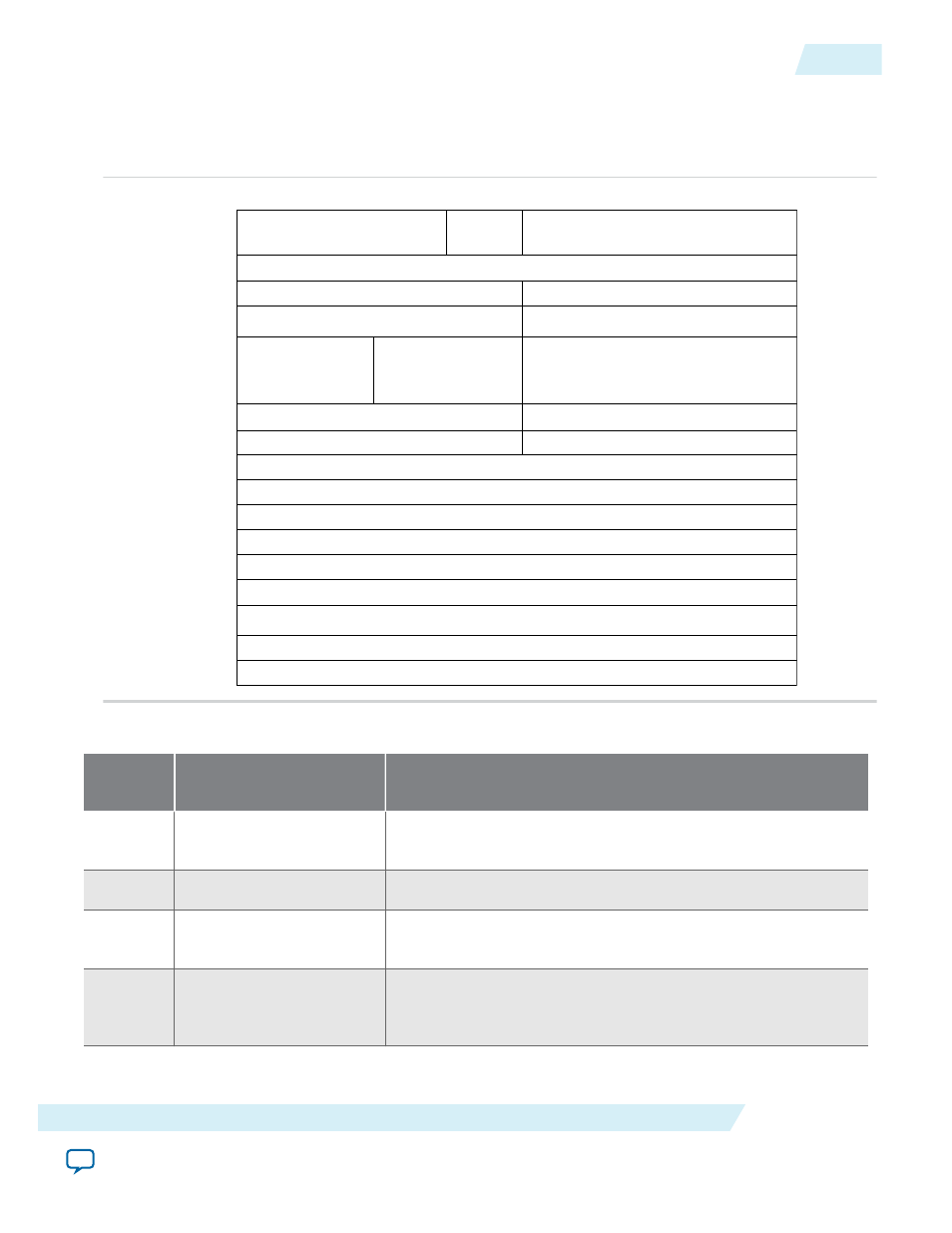

SR-IOV Virtualization Extended Capabilities Registers

Figure 5-6: SR-IOV Virtualization Extended Capabilities Registers

0x180

0x184

0x188

0x18C

0x190

0x194

0x198

0x19C

0x1A0

0x1A4

0x1A8

0x1AC

0x1B0

0x1B4

0x1B8

0x1BC

Next Capability Offset

PCI Express Extended Capability ID

SR-IOV Capabilities

SR-IOV Status

SR-IOV Control

Supported Pages Sizes (RO)

System Page Size (RW)

VF BAR0 (RW)

VF BAR1 (RW)

VF BAR5 (RW)

VF Migration State Array Offset (RO)

31

24 23

16 15

20 19

0

Capability

Version

VF BAR4 (RW)

VF BAR3 (RW)

VF BAR2 (RW)

TotalVFs (RO)

InitialVFs (RO)

RsvdP

NumVFs (RW)

VF Stride (RO)

First VF Offset (RO)

VF Device ID (RO)

RsvdP

Function

Dependency

Link (RO)

Table 5-25: SR-IOV Virtualization Extended Capabilities Registers

Address

(hex)

Name

Description

0x180

SR-IOV Extended Capability

Header

PCI Express Extended Capability ID for SR-IOV and next

capability pointer.

0x184

SR-IOV Capabilities Register Lists supported capabilities of the SR-IOV implementation.

0x188

SR-IOV Control and Status

Registers

The lower 16 bits implement the SR-IOV Control Register. The

upper 16 bits implement the SR-IOV Status Register.

0x18C

InitialVFs/TotalVFs

The lower 16 bits specify the initial number of VFs attached to

PF0. The upper 16 bits specify the total number of PFs available

for attaching to PF0.

UG-01097_sriov

2014.12.15

SR-IOV Virtualization Extended Capabilities Registers

5-17

Registers

Altera Corporation