Altera Stratix V Avalon-ST User Manual

Page 47

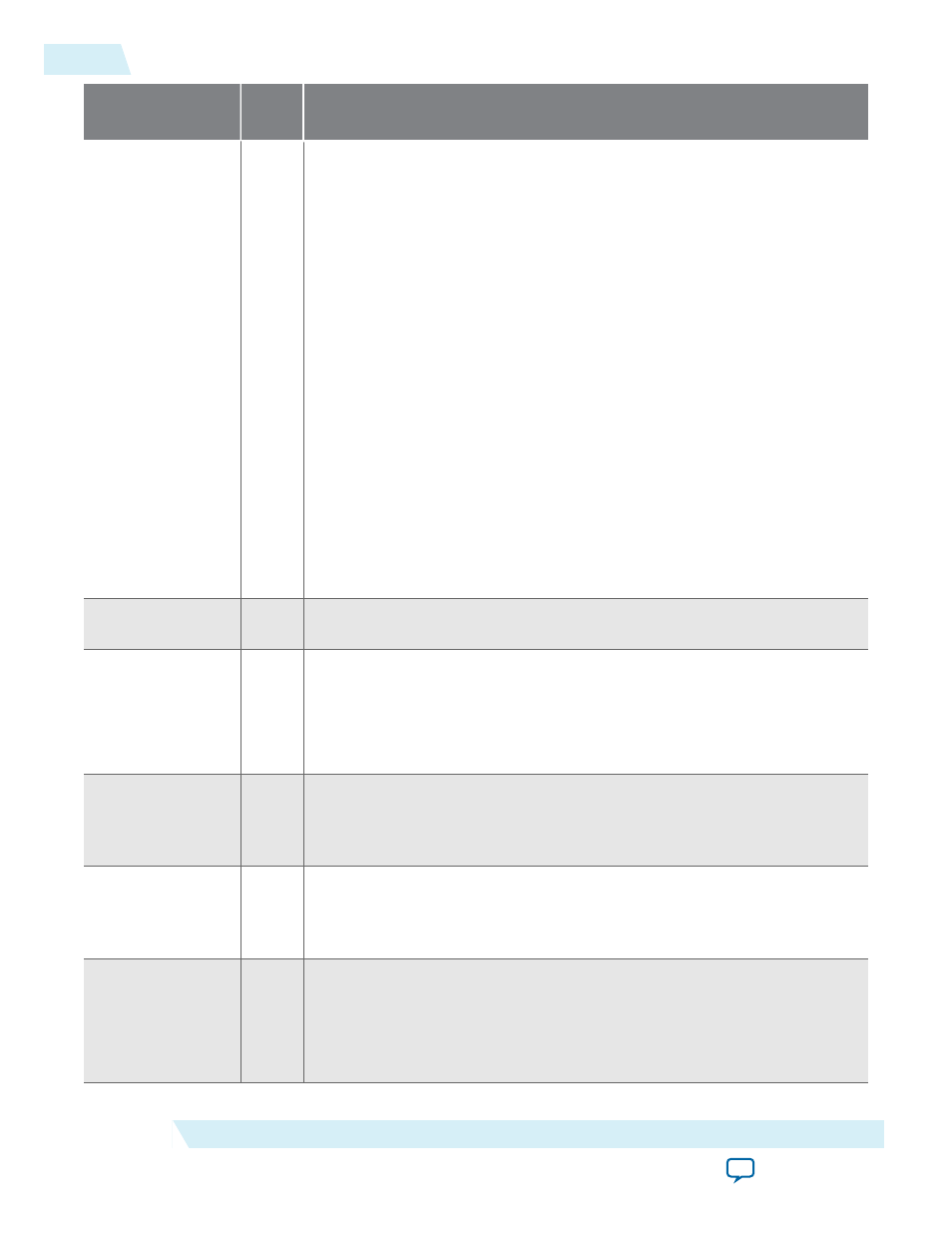

Signal

Directi

on

Description

•

cpl_err[4]

: Unsupported Request (UR) error for posted TLP. The

Application Layer asserts this signal to treat a posted request as an

Unsupported Request. The Hard IP automatically sets the error status bits

in the Configuration Space register and sends error messages in

accordance with the PCI Express Base Specification. Many cases of

Unsupported Requests are detected and reported internally by the

Transaction Layer. For a list of these cases, refer to Transaction Layer

Errors.

•

cpl_err[5]

: Unsupported Request error for non-posted TLP. The

Application Layer asserts this signal to respond to a non-posted request

with an Request (UR) completion. In this case, the Application Layer

sends a completion packet with the Unsupported Request status back to

the requestor, and asserts this error signal. The Hard IP automatically sets

the error status bits in the Configuration Space Register and sends error

messages in accordance with the PCI Express Base Specification. Many

cases of Unsupported Requests are detected and reported internally by the

Transaction Layer. For a list of these cases, refer to Transaction Layer

Errors.

•

cpl_err[6]

: Log header. If header logging is required, this bit must be set

in the every cycle in which any of

cpl_err[2]

,

cpl_err[3]

,

cpl_err[4]

,

or

cpl_err[5]

is set.

cpl_err_

fn[7:0]

Input Specifies the function reporting the error on

cpl_err[6:0]

.

cpl_pending_

pf[1:0]

Input Completion pending. The Application Layer must assert this signal when a

master block associated with PF0 <n> is waiting for a completion. For

example, when a Non-Posted Request is pending from PF0.

cpl_pending_

pf[0]

records pending completions for PF0.

cpl_pending_pf[1]

records

pending completions for PF1.

cpl_pending_

vf[<n>-1:0]

Input Completion pending from VF. The Application Layer must keep bit <n>

asserted when the master block associated with Virtual Function <n> is

waiting for Completion. For example, when a Non-Posted transaction is

pending from VF <n>. <n> is the number of VFs.

log_hdr[127:0]

Input When any of the bits 2, 3, 4, 5 of

cpl_err

is asserted, the Application Layer

may provide the header of the TLP that caused the error condition. The order

of bytes is the same as the order of the header bytes for the Avalon-ST

streaming interfaces.

ko_cpl_spc_

data[11:0]

Output The Application Layer can use this signal to build circuitry to prevent RX

buffer overflow for completion data. Endpoints must advertise infinite space

for completion data; however, RX buffer space is finite.

ko_cpl_spc_data

is

a static signal that reflects the total number of 16 byte completion data units

that can be stored in the completion RX buffer.

4-12

Completion Side Band Signals

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions