Secondary pci express extended capability header – Altera Stratix V Avalon-ST User Manual

Page 97

be designated as prefetchable or non-prefetchable in Qsys. Finally, the address range of VF BAR 0 can be

configured as any power of 2 between 128 bytes and 2 Gbytes.

The contents of VF BAR 0 are described below:

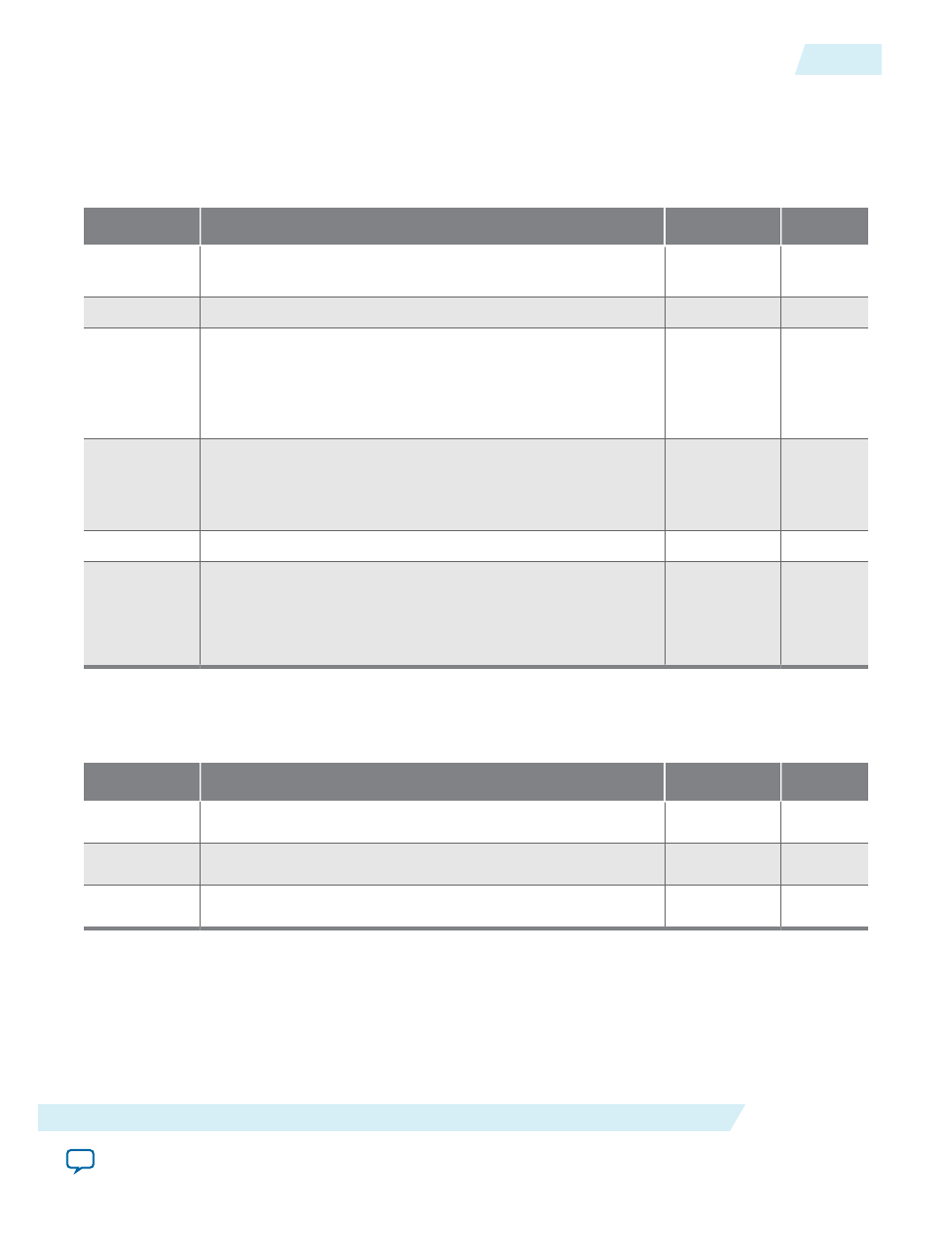

Table 5-37: VF BARs 0 - 5, 0x1A4 - 0x1B0

Bits

Register Description

Default Value

Access

[0]

Memory Space Indicator: Hardwired to 0 to indicate the BAR

defines a memory address range.

0

RO

[1]

Reserved. Hardwired to 0.

0

[2]

Specifies the BAR size.: The following encodings are defined:

• 1'b0: 32-bit BAR

• 1'b1: 64-bit BAR created by pairing BAR0 with BAR1, BAR2

with BAR3, or BAR4 with BAR5

0

RO

[3]

When 1, indicates that the data within the address range refined

by this BAR is prefetchable. When 1, indicates that the data is not

prefetchable. Data is prefetchable if reading is guaranteed not to

have side-effects .

Prefetchable: 0;

Non-Prefetch‐

able: 1

RO

[7:4]

Reserved. Hardwired to 0.

0

RO

[31:8]

Base address of the BAR. The number of writeable bits is based on

the BAR access size. For example, if bits [15:8] are hardwired to 0,

if the BAR access size is 64 Kbytes. Bits [31:16] can be read and

written.

0

See

description

Secondary PCI Express Extended Capability Header

Table 5-38: Secondary PCI Express Extended Capability Header - 0x200

Bits

Register Description

Default Value

Access

[15:0]

PCI Express Extended Capability ID.

0x0019

RO

[19:16]

Capability Version.

0x1

RO

[31:20]

Next Capability Pointer. Points to NULL.

Variable

RO

UG-01097_sriov

2014.12.15

Secondary PCI Express Extended Capability Header

5-23

Registers

Altera Corporation