Lane error status register – Altera Stratix V Avalon-ST User Manual

Page 98

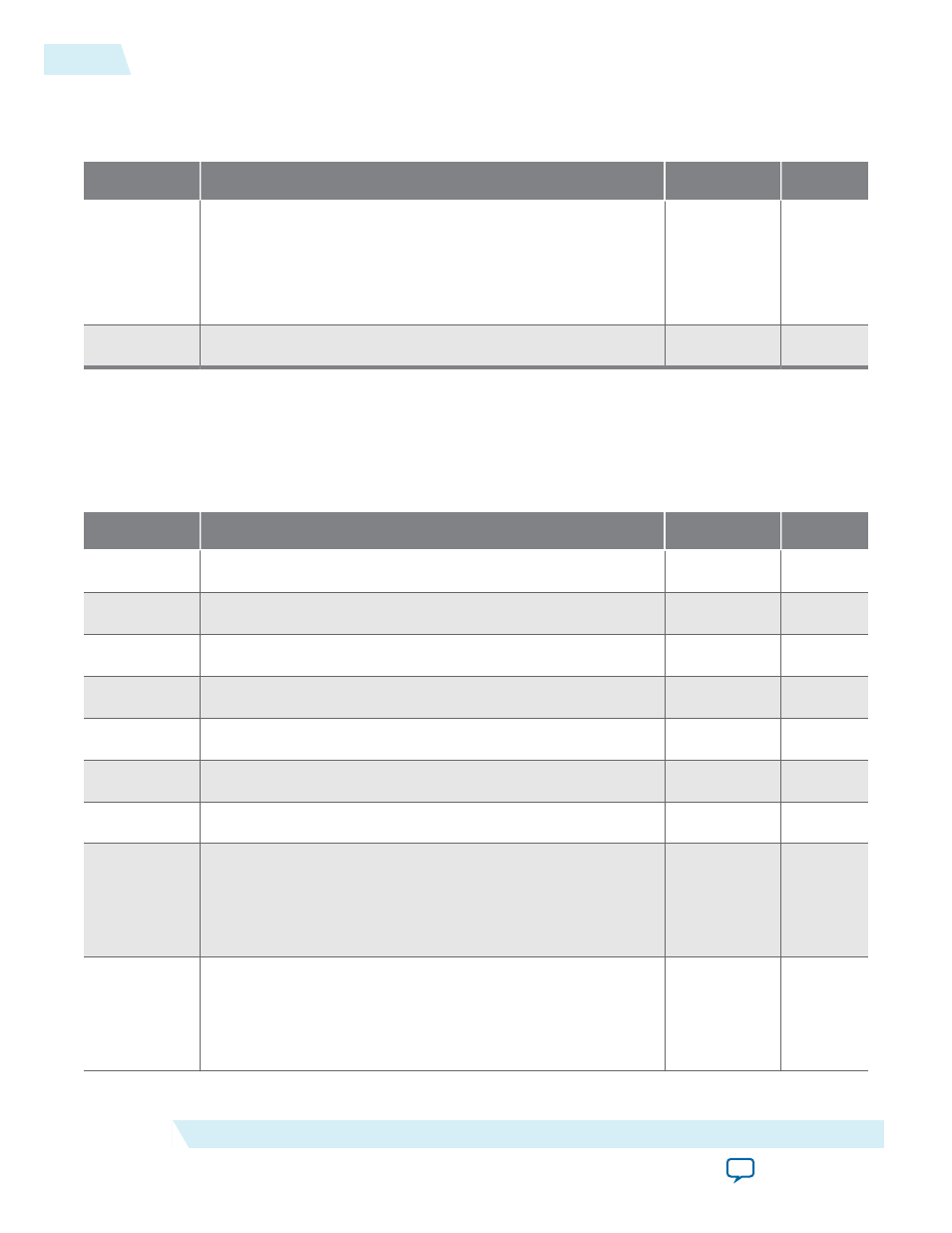

Lane Error Status Register

Table 5-39: Lane Error Status Register - 0x208

Bits

Register Description

Default Value

Access

[7:0]

Lane Error Status: Each 1 indicates an error was detected in the

corresponding lane. Only Bit 0 is implemented when the link

width is 1. Bits [1:0] are implemented when the link width is 2,

and so on. The other bits read as 0. This register is present only in

PF0 when the maximum data rate is 8 Gbps.

0

RW1CS

[31:8]

Reserved

0

RO

Table 5-40: Lane Equalization Control Registers 0–3: 0x20C–0x218

This register contains the Transmitter Preset and the Receiver Preset Hint values. The Training Sequences capture

these values during Link Equalization. This register is present only in PF0 when the maximum data rate is 8 Gbps.

Lane Equalization Control Registers 0 at address 0x20C records values for lanes 0 and 1. Lane Equalization

Control Registers 0 at address 0x20C records values for lanes 2 and 3, and so on.

Bits

Register Description

Default Value

Accress

[6:0]

Reserved

0x7F

RO

[7]

Reserved

0

RO

[11:8]

Upstream Port Lane 0 Transmitter Preset

0xF

RO

[14:12]

Upstream Port Lane 0 Receiver Preset Hint

0x7

RO

[15]

Reserved

0

RO

[22:16]

Reserved

0x7F

RO

[23]

Reserved

0

RO

[27:24]

Upstream Port Lane 1 Transmitter Preset

0xF when link

width > 1

0 when link

width = 1

RO

[30:28]

Upstream Port Lane 1 Receiver Preset Hint

0x7 when link

width > 1

0 when link

width = 1

RO

5-24

Lane Error Status Register

UG-01097_sriov

2014.12.15

Altera Corporation

Registers