Debugging link that fails to reach l0 – Altera Stratix V Avalon-ST User Manual

Page 144

packets can be transmitted. If you encounter link training issues, viewing the actual data in hardware

should help you determine the root cause. You can use the following tools to provide hardware visibility:

• SignalTap II Embedded Logic Analyzer

• Third-party PCIe analyzer

You can use SignalTap II Embedded Logic Analyzer to diagnose the LTSSM state transitions that are

occurring on the PIPE interface. The

ltssmstate[4:0]

bus encodes the status of LTSSM. The LTSSM

state machine reflects the Physical Layer’s progress through the link training process. For a complete

description of the states these signals encode, refer to Status, Link Training and Reset Signals. When link

training completes successfully and the link is up, the LTSSM should remain stable in the L0 state. When

link issues occur, you can monitor

ltssmstate[4:0]

to determine the cause.

Related Information

Reset, Status, and Link Training Signals

Debugging Link that Fails To Reach L0

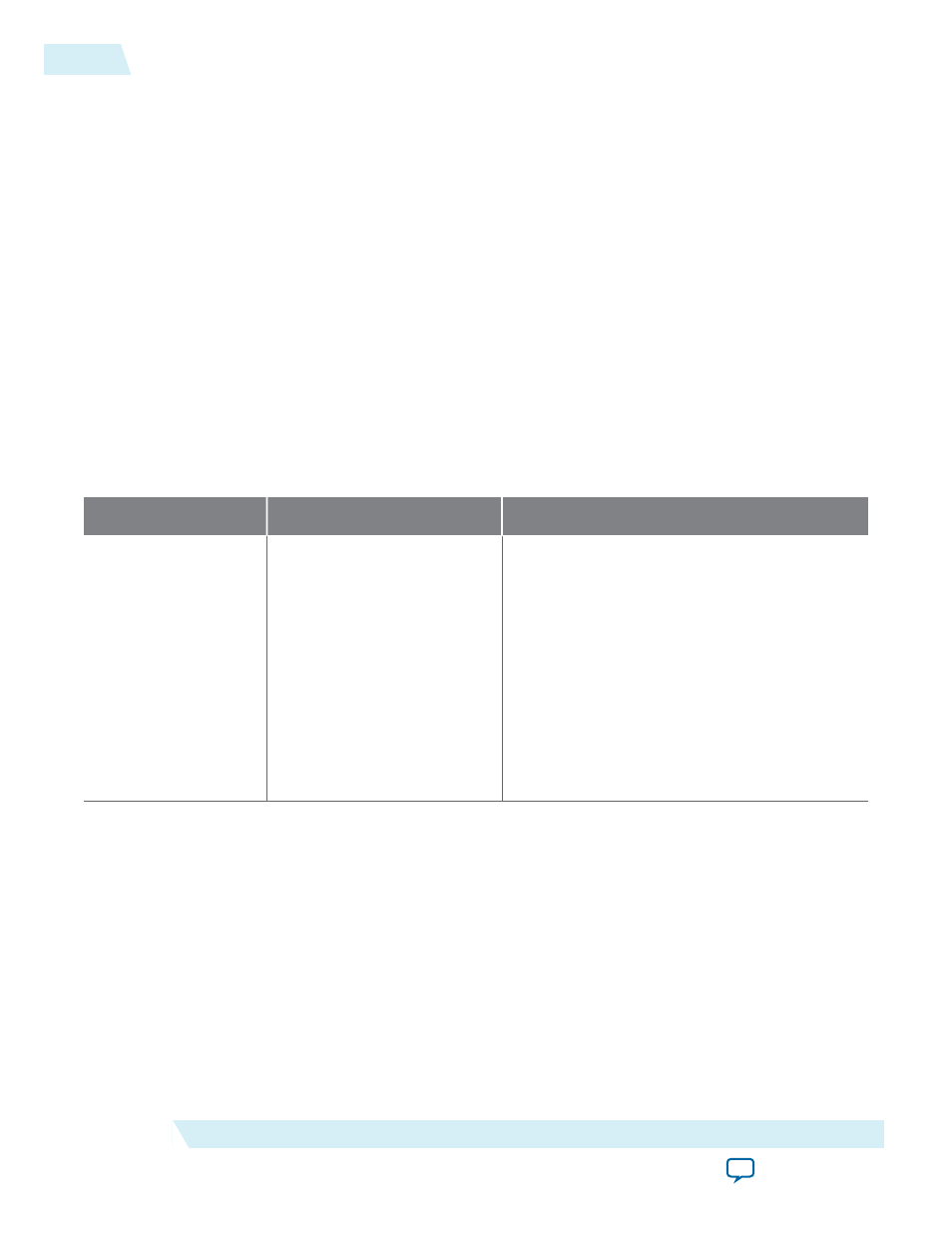

The following table describes possible causes of the failure to reach L0.

Table 12-1: Link Training Fails to Reach L0

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Link fails the

Receiver Detect

sequence.

LTSSM toggles between

Detect.Quiet(0) and

Detect.Active(1) states

Check the following termination settings:

• For Gen1 and Gen2, the PCI Express Base

Specification, Rev 3.0. states a range of 0.075

µF–0.265 µF for on-chip termination (OCT).

• For Gen3, the PCI Express Base Specification,

Rev 3.0 states a range of 0.176 µF–0.265 µF

for OCT.

• Altera uses 0.22 µF terminations to ensure

compliance across all data rates.

• Link partner RX pins must also have

appropriate values for terminations.

12-2

Debugging Link that Fails To Reach L0

UG-01097_sriov

2014.12.15

Altera Corporation

Debugging