Ip core verification, Compatibility testing environment, Performance and resource utilization – Altera Stratix V Avalon-ST User Manual

Page 9

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive verification. The

simulation environment uses multiple testbenches that consist of industry-standard bus functional

models (BFMs) driving the PCI Express link interface. Altera performs the following tests in the

simulation environment:

• Directed and pseudorandom stimuli are applied to test the Application Layer interface, Configuration

Space, and all types and sizes of TLPs

• Error injection tests that inject errors in the link, TLPs, and Data Link Layer Packets (DLLPs), and

check for the proper responses

• PCI-SIG

®

Compliance Checklist tests that specifically test the items in the checklist

• Random tests that test a wide range of traffic patterns

Altera provides the following two example designs that you can leverage to test your PCBs and complete

compliance base board testing (CBB testing) at PCI-SIG.

Related Information

•

•

Compatibility Testing Environment

Altera has performed significant hardware testing to ensure a reliable solution. In addition, Altera

internally tests every release with motherboards and PCI Express switches from a variety of manufac‐

turers. All PCI-SIG compliance tests are run with each IP core release.

Performance and Resource Utilization

Because the PCIe protocol stack is implemented in hardened logic, it uses less than 1% of device

resources.

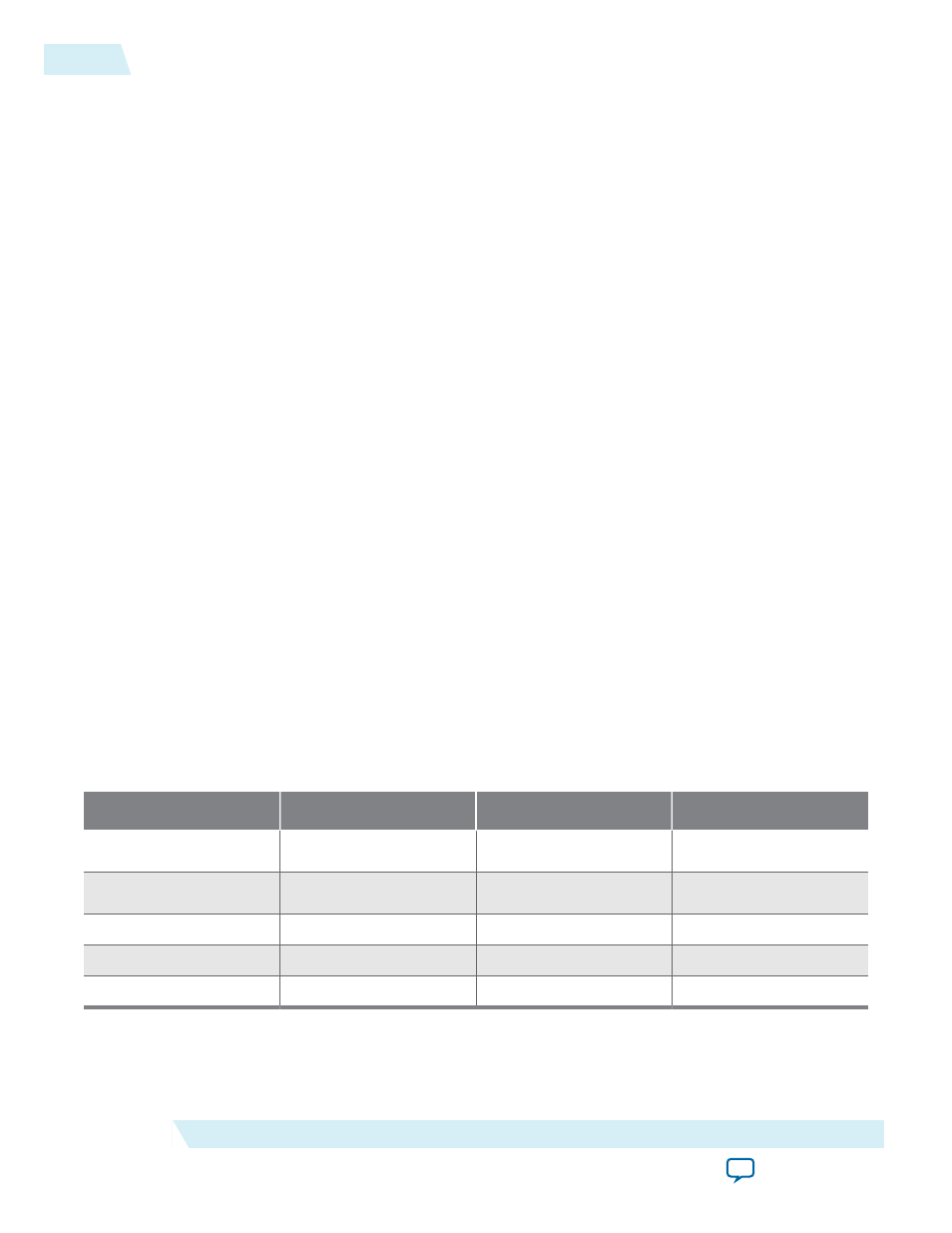

Table 1-5: Performance and Resource Utilization Stratix V Avalon-MM DMA for PCI Express

Number of PFs and VFs

ALMs

M20K Memory Blocks

Logic Registers

2 PFs

2000

14

4800

1 PF, 4 VFs

3000

14

5450

1 PF, 32 VFs

3250

14

5950

2 PFs, 64 VFs

3650

14

6550

2 PFs, 128 VFs

6450

14

9900

Note: Soft calibration of the transceiver module requires additional logic. The amount of logic required

depends upon the configuration.

1-8

IP Core Verification

UG-01097_sriov

2014.12.15

Altera Corporation

Datasheet