Setting up simulation, Changing between serial and pipe simulation – Altera Stratix V Avalon-ST User Manual

Page 146

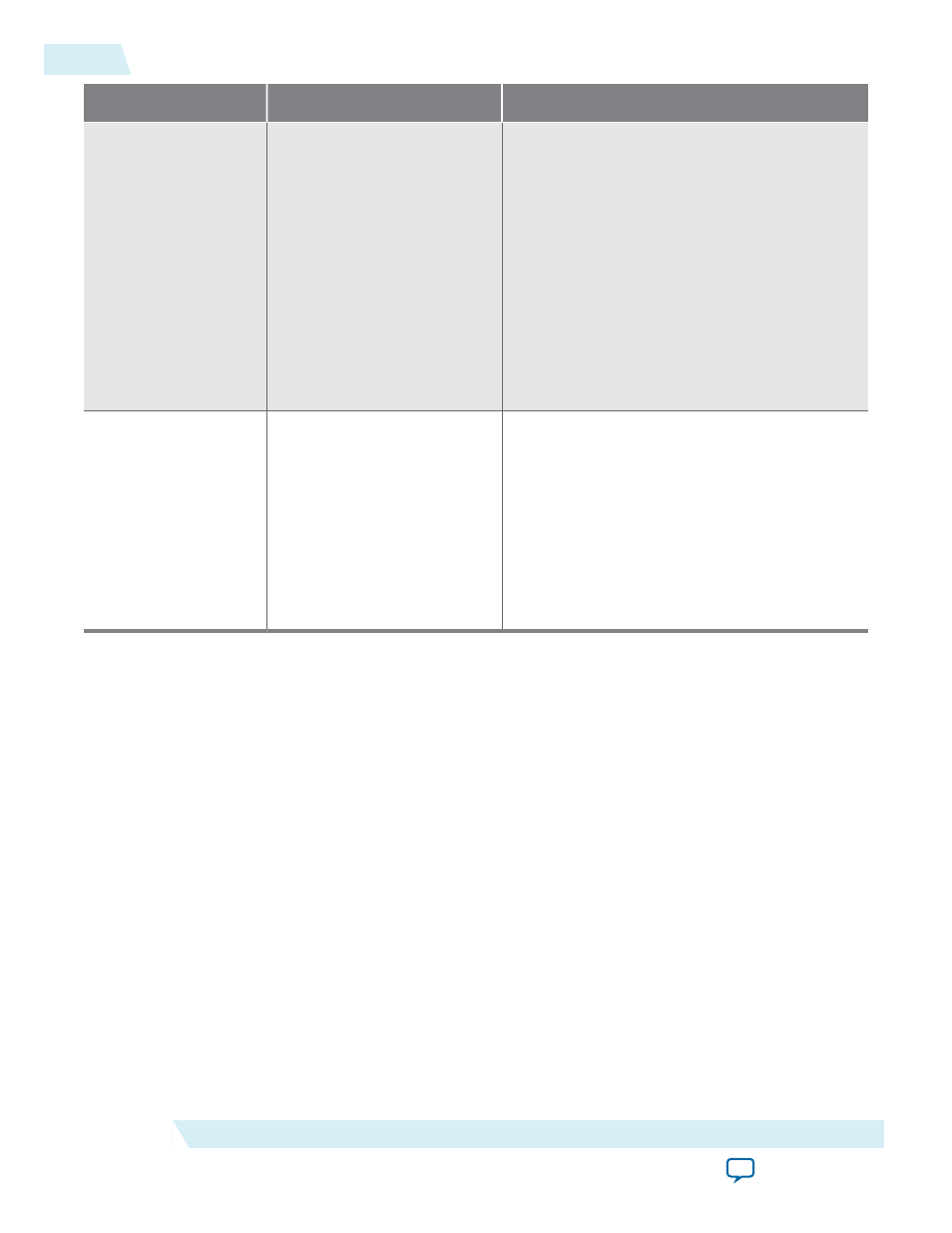

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Link fails due to

unstable

rx_

signaldetect

Confirm that

rx_signaldetect

bus of the active lanes is all 1’s.

If all active lanes are driving all

1’s, the LTSSM state machine

toggles between Detect.Quiet(0),

Detect.Active(1), and

Polling.Active(2) states.

This issue may be caused by mismatches

between the expected power supply to RX side

of the receiver and the actual voltage supplied to

the FPGA from your boards. If your PCB drives

VCCT/VCCR with 1.0 V, you must apply the

following command to both P and N pins of

each active channel to override the default

setting of 0.85 V.

set_instance_assignment -name XCVR_

VCCR_VCCT_VOLTAGE 1_0V –to “pin”

Substitute the pin names from your design for

“pin”

.

Link fails because the

LTSSM state machine

enters Compliance

Confirm that the LTSSM state

machine is in

Polling.Compliance(3) using

SignalTap II.

Possible causes include the following:

• Setting

test_in[6]

=1 forces entry to

Compliance mode when a timeout is reached

in the Polling.Active state.

• Differential pairs are incorrectly connected

to the pins of the device. For example, the

Endpoint’s TX signals are connected to the

RX pins and the Endpoint’s RX signals are to

the TX pins.

Setting Up Simulation

Changing the simulation parameters reduces simulation time and provides greater visibility.

Changing Between Serial and PIPE Simulation

By default, the Altera testbench runs a serial simulation. You can change between serial and PIPE

simulation by editing the top-level testbench file.

The

hip_ctrl_simu_mode_pipe

signal and

enable_pipe32_sim_hwtcl

parameter, specify serial or PIPE

simulation. When both are set to 1'b0, the simulation runs in serial mode. When both are set to 1'b1, the

simulation runs in PIPE mode. Complete the following steps to enable PIPE simulation. These steps

assume that the actual testbench is Gen3 x8 with an Avalon-ST 256-bit interface.:

1. In the top-level testbench, which is

<working_dir>/<variant>/testbench/<variant>_tb/simulation/<variant>_

tb.v

, change the signal,

hip_ctrl_simu_mode_pipe

to 1'b1 as shown:

pcie_de_gen3_x8_ast256 pcie_de_gen3_x8_ast256_inst (.hip_ctrl_simu_mode_pipe

( 1'b1 ),

2. In the top-level HDL module for the Hard IP which is

<working_dir>/<variant>/testbench/<variant>_tb/

simulation/submodules/<variant>.v

change the parameter

enable_pipe32_sim_hwtcl

parameter to 1'b1

as shown:

altpcie_<dev>_hip_ast_hwtcl #( .enable_pipe32_sim_hwtcl ( 1 ),

12-4

Setting Up Simulation

UG-01097_sriov

2014.12.15

Altera Corporation

Debugging