Altera Stratix V Avalon-ST User Manual

Page 51

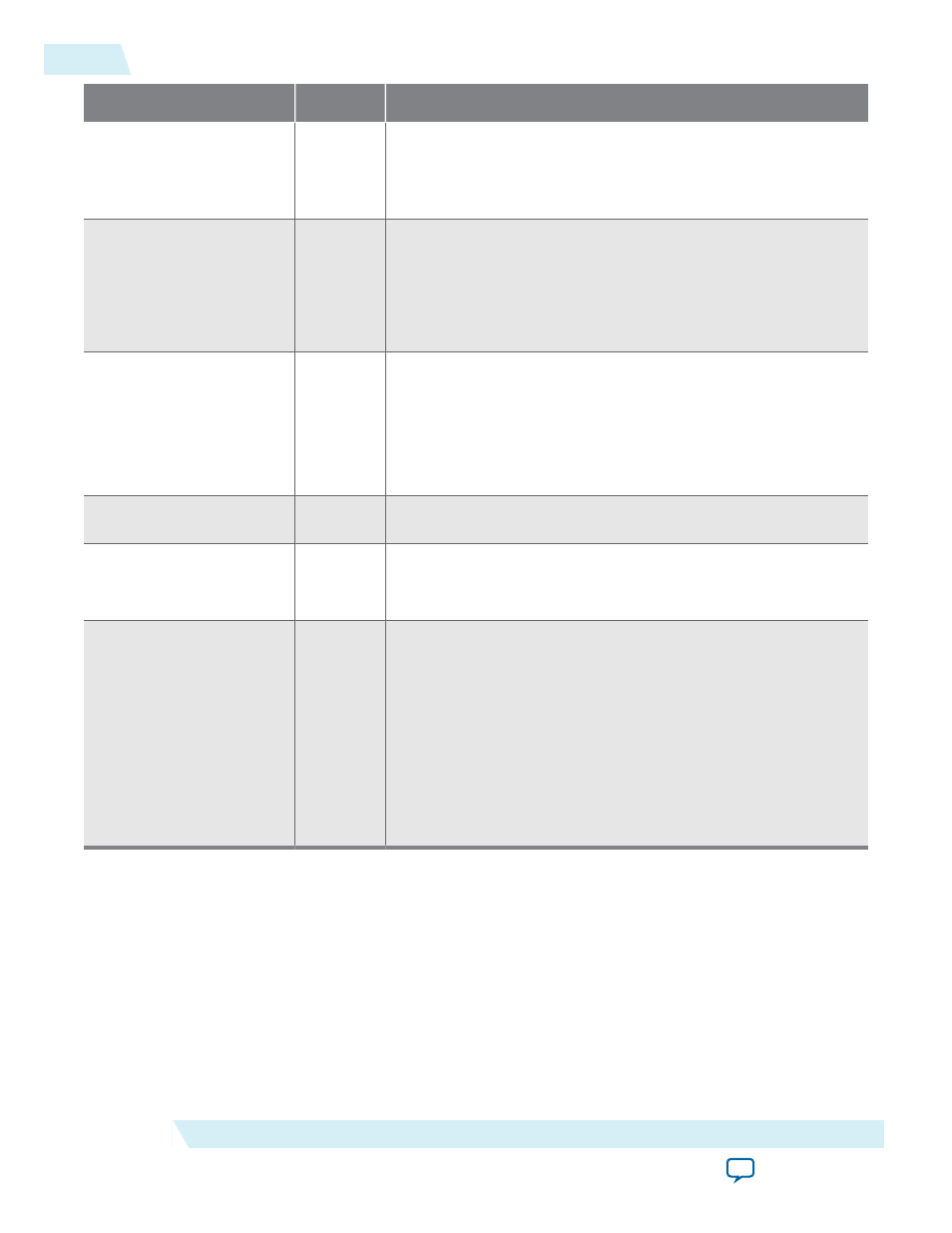

Signal

Direction

Description

app_msi_num[4:0]

Input

Identifies the MSI interrupt type to be generated. Provides the

low-order message data bits to be sent in the message data field

of MSI messages. Only bits that are enabled by the MSI Message

Control Register apply.

app_msi_pending_bit_

write_data

Input

Writes the MSI Pending Bit Register of the specified function

when

msi_pending_bit_write_en

is asserted.

app_msi_

num[4:0]

specifies the bit to be written. For more information

about the MSI Pending Bit Array (PBA), refer to Section 6.8.1.7

Mask Bits for MSI (Optional) in the PCI Local Bus Specification,

Revision 3.0. Refer to

msi_pending_bit_

write_en

Input

Writes a 0 or 1 into selected bit position in the MSI Pending Bit

Register.

app_msi_num[4:0]

specifies the bit to be written.

msi_

pending_bit_write_data

specifies the data to be written (0 or

1).

app_msi_req_fn

specifies the function number.

msi_pending_bit_write_en

cannot be asserted when

app_msi_

req

below.

app_msi_pending_

pf[63:0]

Output

The MSI Data Registers of PF0 and PF1 drive

msi_pending_

pf[63:0]

app_msi_tc[2:0]

Input

Specifies the traffic class to be used to send the MSI or MSI-X

posted write TLP. Must be valid when

app_msi_req

or

app_

msix_req

is asserted.

app_msi_status[1:0]

Output

Indicates the status of an MSI request. Valid when

app_msi_ack

is asserted. The following encodings are defined:

• 2'b00: MSI message sent

• 2'b01: MSI message is pending and not sent upstream because

the MSI mask was set. And, the Pending bit was set for the

MSI number.

• 2/b10: Requested aborted because of invalid parameters. Or,

request aborted because the MSI Enabled bit was not set in

the function's MSI Capability structure.

• 2'b11: Reserved.

4-16

Interrupt Interface

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions