Altera Stratix V Avalon-ST User Manual

Page 88

Bits

Description

Default Value

Access

[31:5]

Reserved

0

RO

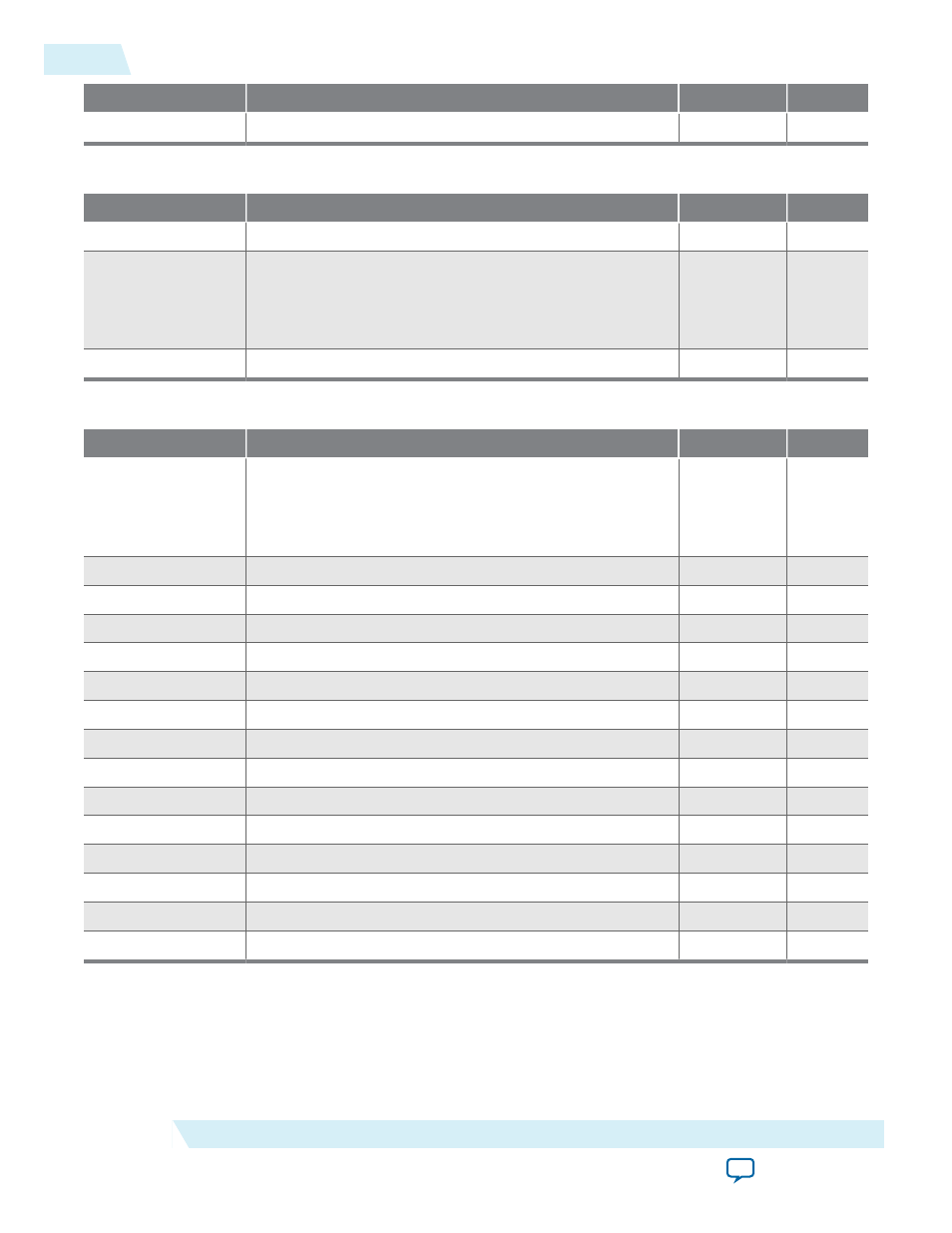

Table 5-19: Link Capabilities 2 Register - 0x0AC

Bits

Description

Default Value

Access

[0]

Reserved

0

RO

[3:1]

Link speeds supported

1 (2.5 GT/s)

3 (5.0 GT/s)

7 (8.0 GT/s)

RO

[31:4]

Reserved

0

RO

Table 5-20: Link Control and Status 2 Register - 0x0B0

Bits

Description

Default Value

Access

[3:0]

Target Link Speed

1: Gen1

2: Gen2

3: Gen3

RWS

[4]

Enter Compliance

0

RWS

[5]

Hardware Autonomous Speed Disable

0

RW

[6]

Selectable De-emphasis

0

RO

[9:7]

Transmit Margin

0

RWS

[10]

Enter Modified Compliance

0

RWS

[11]

Compliance SOS

0

RWS

[15:12]

Compliance Preset/De-emphasis

0

RWS

[16]

Current De-emphasis Level

0

RO

[17]

Equalization Complete

0

RO

[18]

Equalization Phase 1 Successful

0

RO

[19]

Equalization Phase 2 Successful

0

RO

[20]

Equalization Phase 3 Successful

0

RO

[21]

Link Equalization Request

0

RW1C

[31:22]

Reserved

0

RO

5-14

PCI Express Capability Structure

UG-01097_sriov

2014.12.15

Altera Corporation

Registers