Vf device id register, Vf base address registers (bars) 0-5, Page size registers – Altera Stratix V Avalon-ST User Manual

Page 96

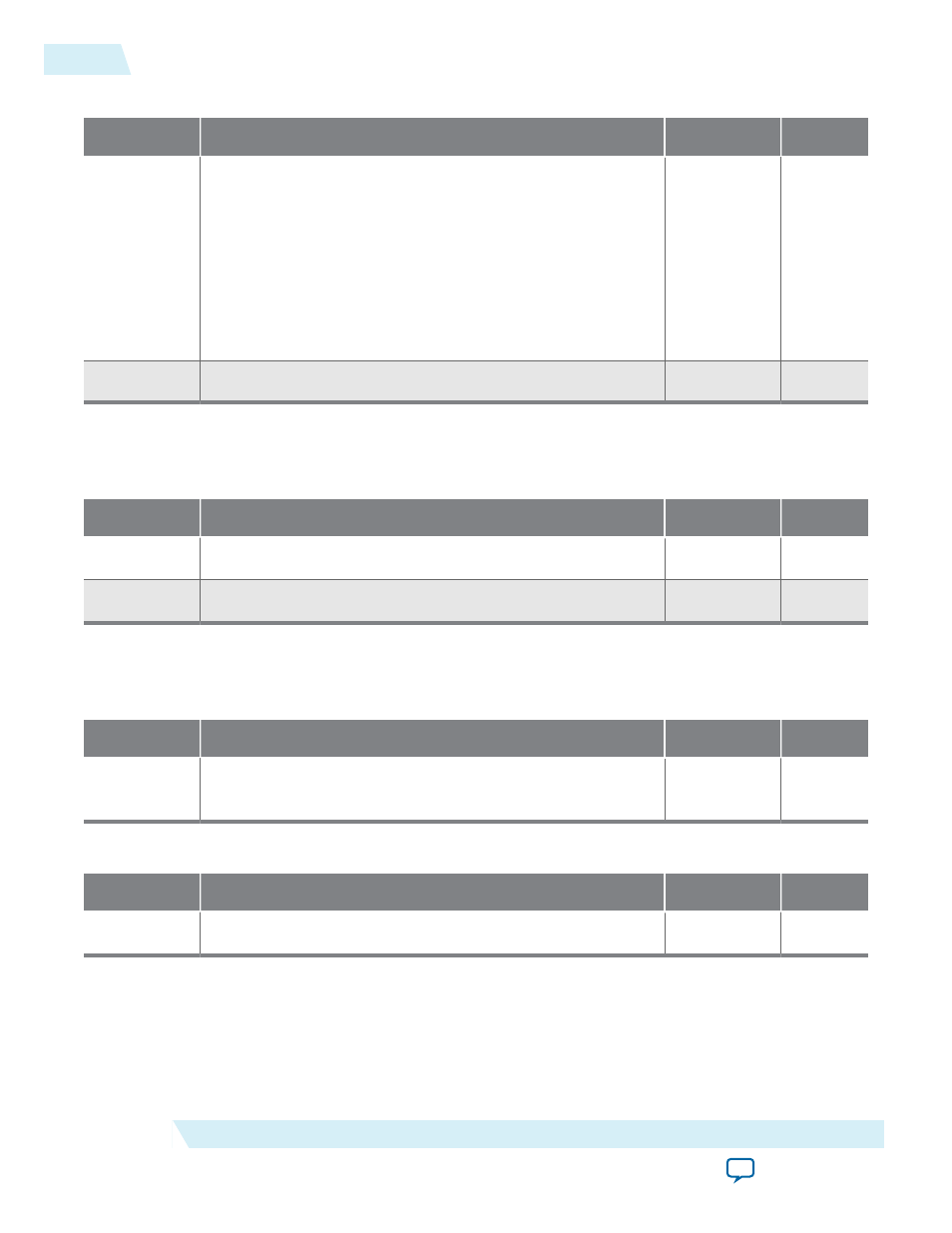

Table 5-33: VF Offset and Stride Registers - 0x194

Bits

Register Description

Default Value

Access

[15:0]

VF Offset. Specifies the offset of the first VF’s Routing ID with

respect to the Routing ID of its PF. The offset is configured for

PF0 and PF1 based on the number of VFs and whether ARI is in

use. The following offsets are used:

• Single-Function with no ARI: VF Offset = 1.

• Two PFs with no ARI: VF Offset = 2 for PF0.

1+ PF0_VF_

COUNT

for PF1.

• With ARI: VF Offset = 128 for PF 0.

127+ PF0_VF_COUNT

for

PF 1.

Refer to

description

RO

[31:16]

VF Stride

1

RO

VF Device ID Register

Table 5-34: VF Device ID Register - 0x198

Bits

Register Description

Default Value

Access

[15:0]

Reserved

0

RO

[31:16]

VF Device ID

Set in Qsys

RO

Page Size Registers

Table 5-35: Supported Page Size Register - 0x19C

Bits

Register Description

Default Value

Access

[31:0]

Supported Page Sizes. Specifies the page sizes supported by the

device

Set in Qsys

RO

Table 5-36: System Page Size Register - 0x1A0

Bits

Register Description

Default Value

Access

[31:0]

Supported Page Sizes. Specifies the page size currently in use.

Set in Qsys

RO

VF Base Address Registers (BARs) 0-5

Each PF implements six BARs. You specify BAR settings in Qsys. You can configure VF BARs as 32-bit

memories. Or you can combine VF BAR0 and BAR1 to form a 64-bit memory BAR. VF BAR 0 may also

5-22

VF Device ID Register

UG-01097_sriov

2014.12.15

Altera Corporation

Registers