Advanced error capabilities and control register, Vf base address registers (bars) 0-5 – Altera Stratix V Avalon-ST User Manual

Page 93

Address

(hex)

Name

Description

0x210

Lane Equalization Control

Register 1

Transmitter Preset and Receiver Preset Hint values for Lanes 2

and 3 of remote device. These values are captured during Link

Equalization.

0x214

Lane Equalization Control

Register 2

Transmitter Preset and Receiver Preset Hint values for Lanes 4

and 5 of remote device. These values are captured during Link

Equalization.

0x218

Lane Equalization Control

Register 3

Transmitter Preset and Receiver Preset Hint values for Lanes 6

and 7 of remote device. These values are captured during Link

Equalization.

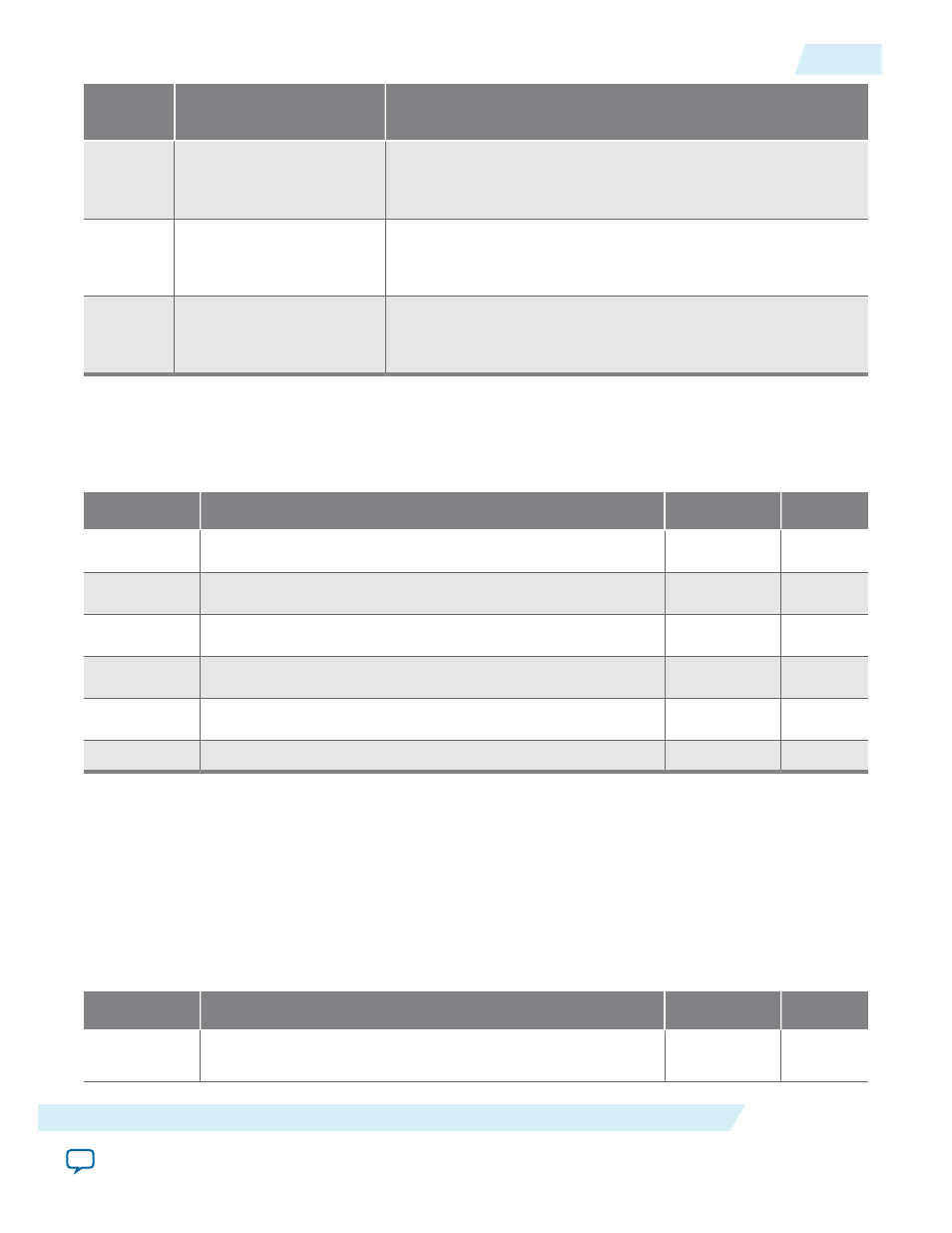

Advanced Error Capabilities and Control Register

Table 5-26: Advanced Error Capabilities and Control Register - 0x158 (ARI supported) or 0x118 (ARI not

supported)

Bits

Register Description

Default Value

Access

[4:0]

First Error Pointer

0

ROS

[5]

ECRC Generation Capable

Set in Qsys

RO

[6]

ECRC Generation Enable

0

RW

[7]

ECRC Check Capable

Set in Qsys

RO

[8]

ECRC Check Enable

0

RW

[31:9]

Reserved

0

RO

VF Base Address Registers (BARs) 0-5

Each PF implements six BARs. You can specify BAR settings in Qsys. You can configure VF BARs as 32-

bit memories. Or you can combine VF BAR0 and BAR1 to form a 64-bit memory BAR. VF BAR 0 may

also be designated as prefetchable or non-prefetchable in Qsys. Finally, the address range of VF BAR 0 can

be configured as any power of 2 between 128 bytes and 2 Gbytes.

The contents of VF BAR 0 are described below:

Table 5-27: VF BARs 0 - 5, 0x1A4 - 1B0

Bits

Register Description

Default Value

Access

[0]

Memory Space Indicator: Hardwired to 0 to indicate the BAR

defines a memory address range.

0

RO

UG-01097_sriov

2014.12.15

Advanced Error Capabilities and Control Register

5-19

Registers

Altera Corporation