Understanding the generated files and directories, Simulating the sr--iov example design, Running a gate-level simulation – Altera Stratix V Avalon-ST User Manual

Page 16

Parameter

Value

Path

working_dir/top

10.Click Generate.

11.On the File menu, click Save.

Understanding the Generated Files and Directories

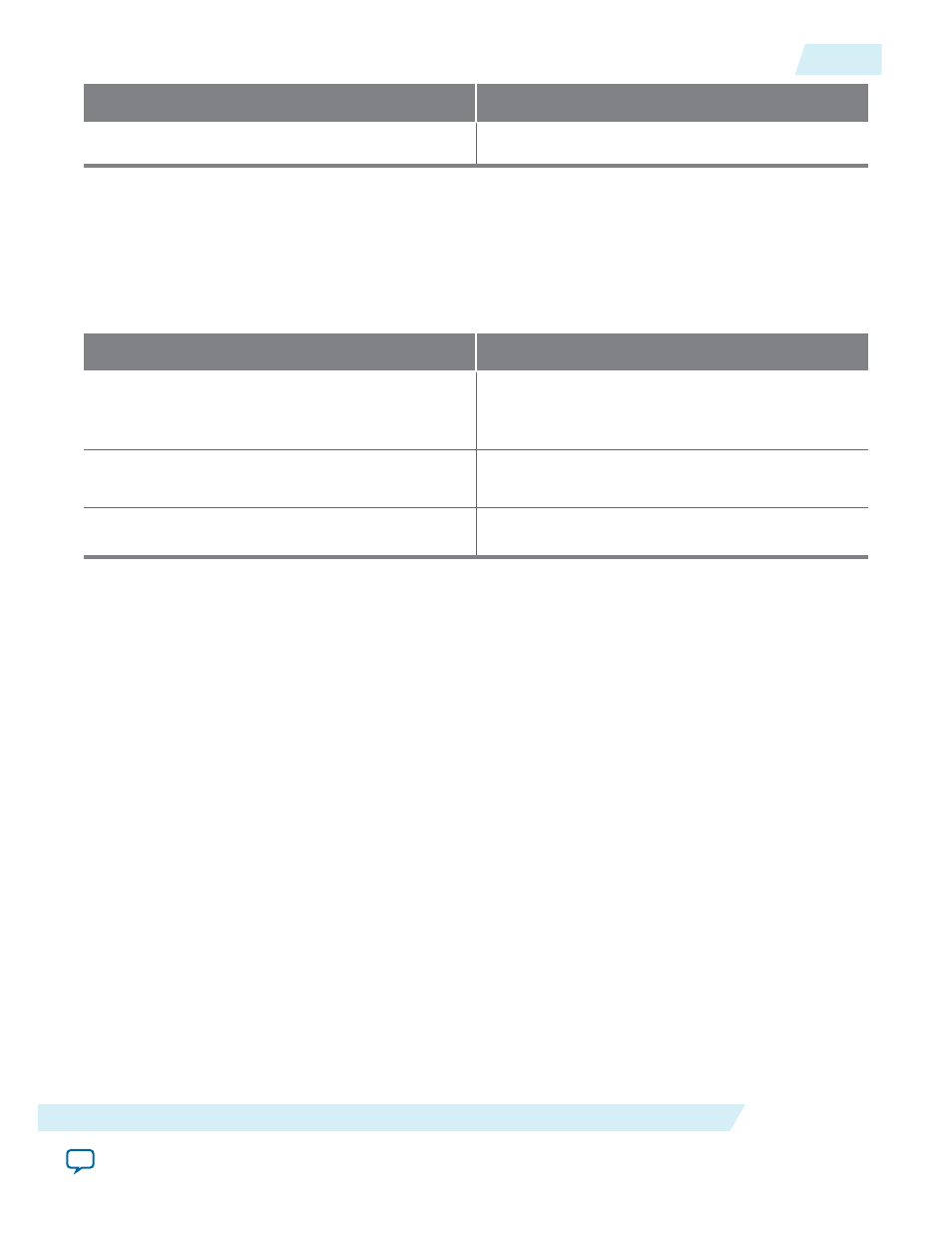

Table 2-3: Qsys Generation Output Files

Directory

Description

<testbench_dir>/<variant_name>/testbench

Includes testbench subdirectories for the Aldec,

Cadence, Mentor, and Synopsys simulation tools

with the required libraries and simulation scripts.

<testbench_dir>/<variant_name>/testbench/<cad_

vendor>

Includes the HDL source files and scripts for the

simulation testbench.

<testbench_dir>/<variant_name>/testbench/<variant_

name>_tb/simulation/submodules

Includes the HDL files for simulation.

Simulating the SR--IOV Example Design

Follow these steps to simulate the Qsys system using ModelSim:

1. In a terminal window, change to the

<working_dir>/sim/mentor

directory.

2. Start the ModelSim simulator by typing

vsim

.

3. To compile the simulation, type the following commands in the terminal window:

•

do msim_setup.tcl

(The

msim_setup.tcl

file defines aliases.

•

ld_debug

(The

ld_debug

command argument stops optimizations, improving visibility in the

ModelSim waveforms. )

•

run -all

Running A Gate-Level Simulation

The PCI Express testbenches run simulations at the register transfer level (RTL). However, it is possible to

create you own gate-level simulations. Contact your Altera Sales Representative for instructions and an

example that illustrate how to create a gate-level simulation from the RTL testbench.

UG-01097_sriov

2014.12.15

Understanding the Generated Files and Directories

2-5

Getting Started with the SR-IOV DMA Example Design

Altera Corporation