Altera Stratix V Avalon-ST User Manual

Page 53

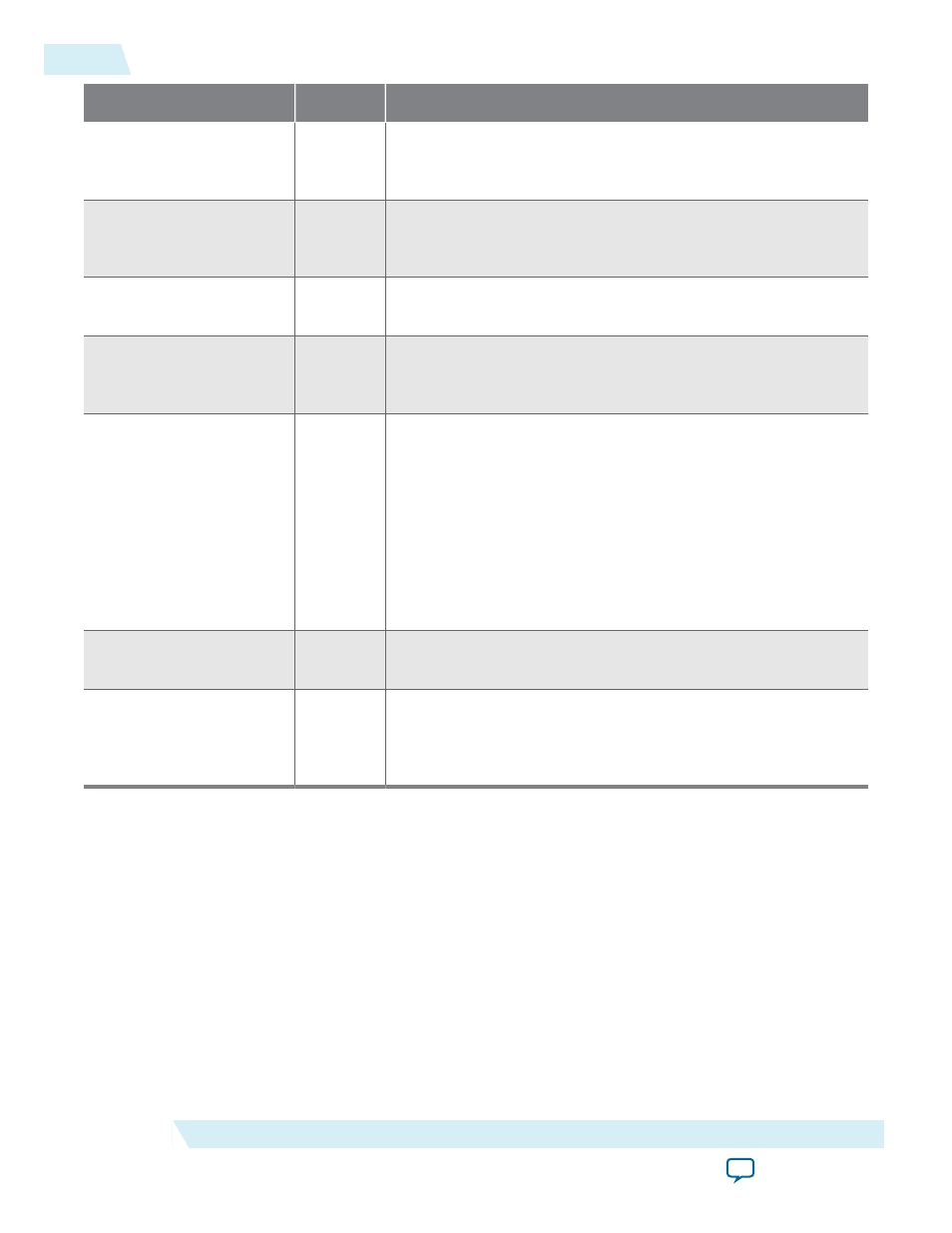

Signal

Direction

Description

app_msix_addr[63:0]

Input

The Application Layer drives the address for the MSI-X posted

write TLP on this input. Driven in the same cycle as

app_msix_

req

.

app_msix_data[31:0]

Input

The Application Layer drives

app_msix_data[31:0]

for the

MSI-X posted write TLP. Driven in the same cycle as

app_msix_

req

.

app_msix_enable_

pf[1:0]

Output

The MSI-X Enable bit of PF0 and PF1 MSI-X Control Register

drive this output.

app_msix_enable_

vf[<n>-1:0]

Output

The MSI-X Enable bit of the MSI-X Control Register for VF0

drives bit[0]. The MSI-X Enable bit of the MSI-X Control

Register for VF1 drives bit[1], and so on.

app_msix_err

Output

Indicates an error during the execution of an MSI-X request.

Valid when

app_msix_ack

is asserted. The following encodings

are defined:

• 1b'0: MSI-X message sent

• 1b'1: Error detected during execution of the MSI-X request.

No message sent. The following errors may occur:

• The function number is invalid

• The MSI-X Enable bit for the function was not set

• The MSI-X Function Mask was not set

app_msix_fn_mask_

pf[1:0]

Output

The MSI-X Function Mask bit of PF0 and PF1 MSI-X Control

Register drive this output.

app_msix_fn_mask_

vf[<n>-1:0]

Output

The MSI-X Function Mask bit of the MSI-X Control Register for

VF0 drives bit[0]. The MSI-X Function Mask bit of the MSI-X

Control Register for VF1 drives bit[1], and so on. <n> equals the

total number of VFs for both PF0 and PF1.

4-18

Interrupt Interface

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions