Altera Stratix V Avalon-ST User Manual

Page 105

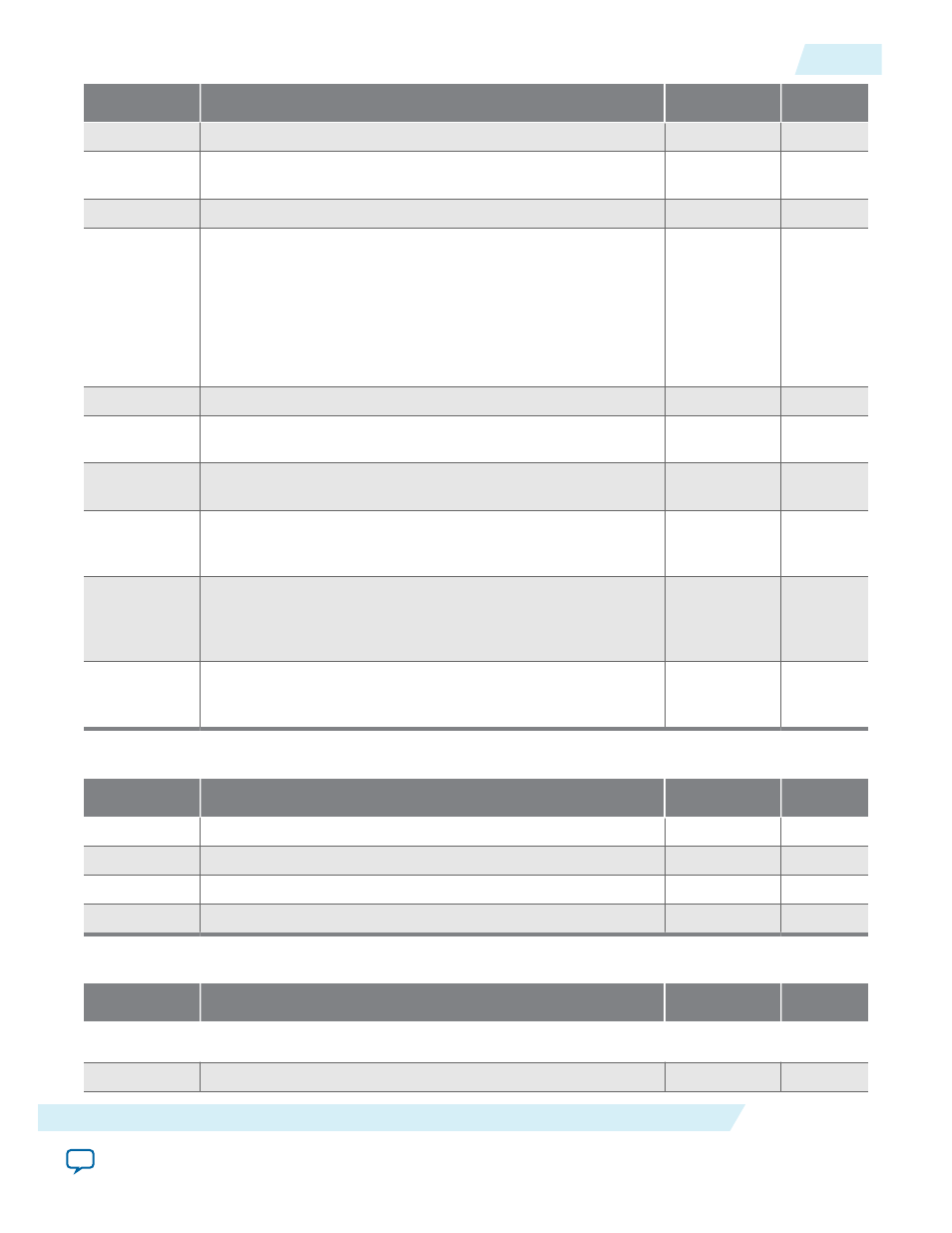

Bits

Register Description

Default Value

Access

[3:0]

Reserved.

0

RO

[4]

Indicates the presence of PCI Extended Capabilities. This bit is

hardwired to 1.

0

RW1C

[7:5]

Reserved.

0

RO

[8]

Master Data Parity Error. Enabled when the PF PCI Command

Register Parity Error Response bit is set. When set, indicates one

of the following conditions:

• The device has received a Poisoned Completion from the link

for this VF

• This VF has transmitted a Poisoned Memory Write request on

the link

RW1C

[10:9]

Reserved.

0

RO

[11]

Signal Target Abort. When set, this VF has sent a Completion to

the link with Completer Abort (CA) stats.

0

RW1C

[12]

Received Target Abort. When set, indicates that this VF has

received a Completion from the link with the CA status.

0

RW1C

[13]

Received Master Abort. When set, indicates that this VF has

received a Completion from the link with the Unsupported

Request (UR) status.

0

RW1C

[14]

Signaled System Error. When set, indicates that this VF has

transmitted a Fatal or Non-Fatal error message on the link to the

Root Complex. Enabled when the PF PCI Command Register

SERR Enable bit is set.

0

RW1C

[15]

Received Master Abort. When set, indicates the VF has received a

Completion from the link with the Unsupported Request (UR)

status.

0

RW1C

Table 5-48: PCI Express Capability List Register for VFs

Bits

Register Description

Default Value

Access

[31:19]

Hardwired to 0.

0

RO

[18:16]

Version ID: Version of PCI Express Capability.

2

RW

[15:8]

Next Capability Pointer: Points to NULL.

0

RO

[7:0]

Capability ID assigned by PCI-SIG.

0x10

RO

Table 5-49: PCI Express Device Control and Status Registers for VFs

Bits

Register Description

Default Value

Access

Control Register

[14:0]

Reserved.

0

RO

UG-01097_sriov

2014.12.15

Virtual Function Registers

5-31

Registers

Altera Corporation