Altera Stratix V Avalon-ST User Manual

Page 50

This interface also includes signals to set and clear the individual bits in the MSI Pending Bit Register.

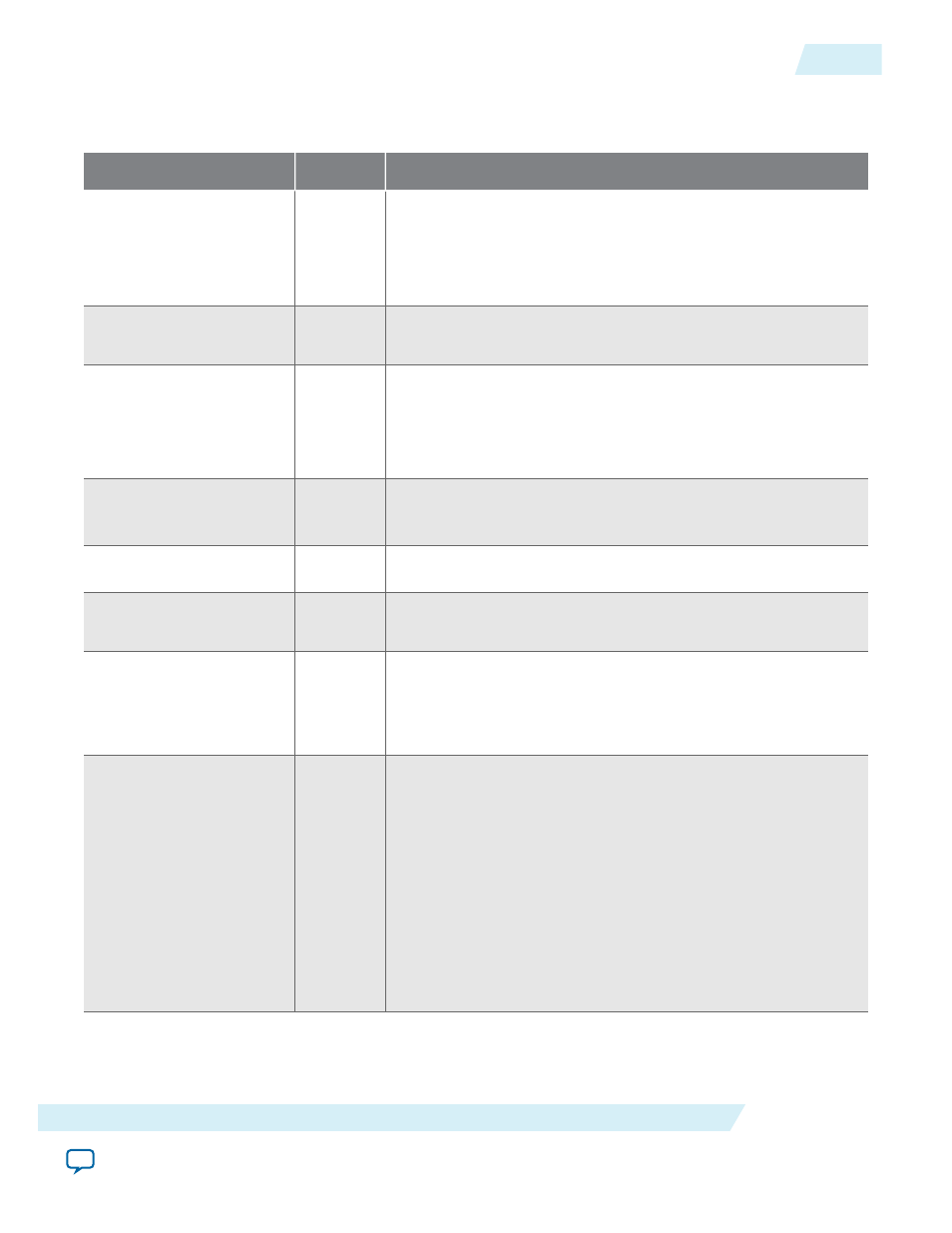

Table 4-8: MSI Interrupts

Signal

Direction

Description

app_msi_req

Input

When asserted, the Application Layer is requesting that an MSI

interrupt be sent. Assertion causes an MSI posted write TLP to be

generated. The MSI TLP uses

app_msi_req_fn[7:0]

,

app_msi_

tc

and

app_msi_num

for a

timing diagram.

app_msi_req_fn[7:0]

Input

Specifies the function generating the MSI or MSI-X interrupt.

Driven in the same cycle as

app_msi_req

or

app_msix_req

.

app_msi_ack

Output

Ack for MSI interrupts. When asserted, indicates that Hard IP

has sent an MSI posted write TLP in response

app_msi_req

. The

Application Layer must wait for

app_msi_ack

after asserting

app_msi_req

. The Application Layer must de-assert

app_msi_

req

for at least 1 cycle before signaling a new MSI interrupt.

app_msi_addr_

pf[127:0]

Output

Driven by the MSI address registers of PF0 and PF1.

app_msi_

addr_pf[63:0]

specifies the PF0 address.

app_msi_addr_

pf[127:64]

specifies the PF1 address.

app_msi_data_pf[16<n>

-1:0]

Output

Driven by the MSI Data Registers of PF0 and PF1. <n>= the

number of PFs.

app_msi_enable_

pf[1:0]

Output

Driven by the MSI Enable bit of the MSI Control Registers of PF0

and PF1.

app_msi_mask_pf[32<n>

-1:0]

Output

The MSI Mask Bits of the MSI Capability Structure drive

app_

msi_mask_pf

. This mask allows software to disable or defer

message sending on a per-vector basis.

app_msi_mask_pf[31:0]

mask vectors for PF0.

app_msi_mask_pf[63:32]

mask vectors

for PF1.

app_msi_multi_msg_

enable_pf[5:0]

Output

Defines the number of interrupt vectors enabled for each PF. The

following encodings are defined:

• 3'b000: 1 vector

• 3'b001: 2 vectors

• 3'b010: 4 vectors

• 3'b100: 16 vectors

• 3'b101: 32 vectors

The MSI Multiple Message Enable field of the MSI Control

Register of PF0 drives

app_msi_multi_msg_enable_pf[2:0]

.

The MSI Multiple Message Enable field of the MSI Control

Register of PF1 drives

app_msi_multi_msg_enable_pf[5:3]

.

UG-01097_sriov

2014.12.15

Interrupt Interface

4-15

Interfaces and Signal Descriptions

Altera Corporation