Altera Stratix V Avalon-ST User Manual

Page 86

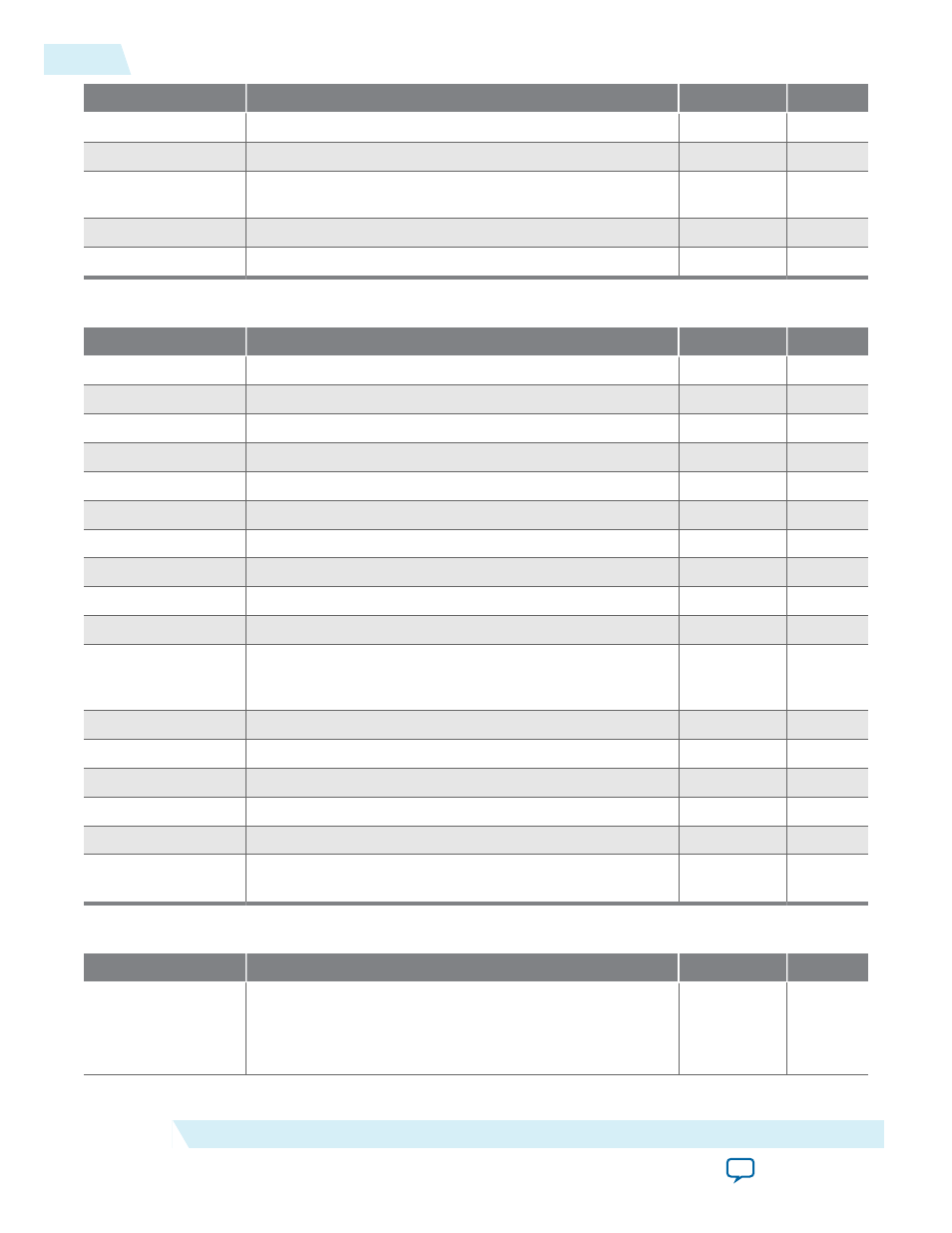

Bits

Description

Default Value

Access

[15]

Role-Based error reporting supported

1

RO

[17:16]

Reserved

0

RO

[27:18]

Captured Slot Power Limit Value and Scale: Not

implemented

0

RO

[28]

FLR Capable. Indicates that the device has FLR capability

Set in Qsys

RO

[31:29 ]

Reserved

0

RO

Table 5-14: PCI Express Device Control and Status Register - 0x088

Bits

Description

Default Value

Access

[0

Enable Correctable Error Reporting.

0

RW

[1]

Enable Non-Fatal Error Reporting.

0

RW

[2]

Enable Fatal Error Reporting.

0

RW

[3]

Enable Unsupported Request (UR) Reporting.

0

RW

[4]

Enable Relaxed Ordering.

Set in Qsys

RW

[7:5]

Maximum Payload Size.

0 (128 bytes)

RW

[8]

Extended Tag Field Enable.

0

RW

[10:9]

Reserved.

0

RO

[11]

Enable No-Snoop.

1

RW

[14:12]

Maximum Read Request Size.

2 (512 bytes)

RW

[15]

Function-Level Reset. Writing a 1 generates a Function-Level

Reset for this Function if the FLR Capable bit of the Device

Capabilities Register is set. This bit always reads as 0.

0

RW

[16]

Correctable Error detected.

0

RW1C

[17]

Non-Fatal Error detected.

0

RW1C

[18]

Fatal Error detected.

0

RW1C

[19]

Unsupported Request detected.

0

RW1C

[20]

Reserved.

0

RO

[21]

Transaction Pending: Indicates that a Non- Posted request

issued by this Function is still pending.

0

RO

Table 5-15: Link Capabilities Register - 0x08C

Bits

Description

Default Value

Access

[3:0]

Maximum Link Speed

1: 2.5 GT/s

2: 5.0 GT/s

3: 8.0 GT/s

RO

5-12

PCI Express Capability Structure

UG-01097_sriov

2014.12.15

Altera Corporation

Registers