Altera Stratix V Avalon-ST User Manual

Page 87

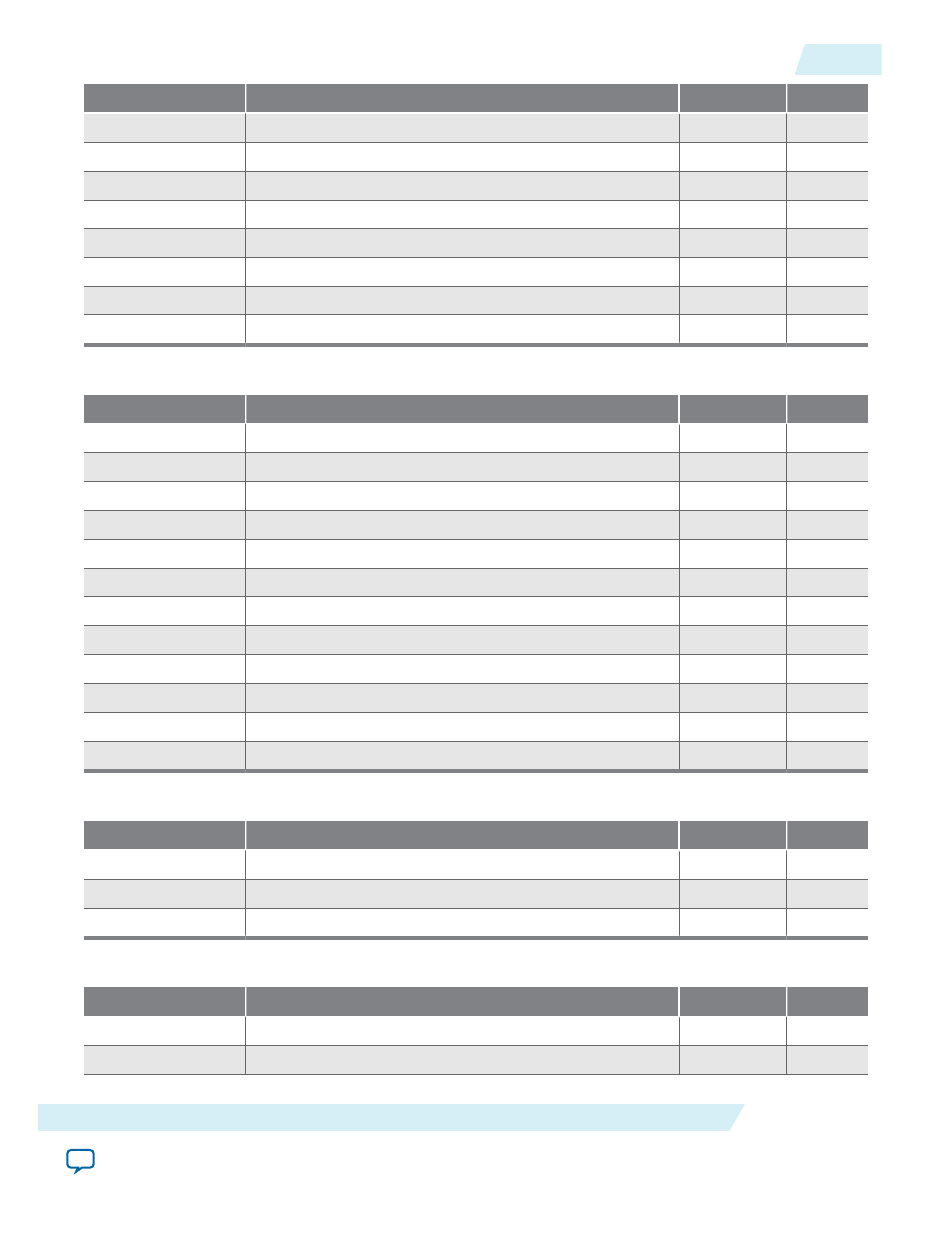

Bits

Description

Default Value

Access

[9:4]

Maximum Link Width

1, 2, 4 or 8

RO

[10]

ASPM Support for L0S state

0

RO

[11]

ASPM Support for L1 state

0

RO

[14:12]

L0S Exit Latency

0x6

RO

[17:15]

L1 Exit Latency

0

RO

[21:18]

Reserved

0

RO

[22]

ASPM Optionality Compliance

1

RO

[31:23]

Reserved

0

RO

Table 5-16: Link Control and Status Register - 0x090

Bits

Description

Default Value

Access

[1:0]

ASPM Control

0

RW

[2]

Reserved

0

R O

[3]

Read Completion Boundary

0

RW

[5:4]

Reserved

0

RO

[6]

Common Clock Configuration

0

RW

[7]

Extended Synch

0

RW

[15:8]

Reserved

0

RO

[19:16]

Negotiated Link Speed

0

RO

[25:20]

Negotiated Link Width

0

RO

[27:26]

Reserved

0

RO

[28]

Slot Clock Configuration

1

RO

[31:29]

Reserved

0

RO

Table 5-17: PCI Express Device Capabilities 2 Register - 0x0A4

Bits

Description

Default Value

Access

[3:0]

Completion Timeout ranges

0xF

RO

[4]

Completion Timeout disable supported

1

RO

[31:5]

Reserved

0

RO

Table 5-18: PCI Express Device Control and Status 2 Register - 0x0A8

Bits

Description

Default Value

Access

[3:0]

Completion Timeout value

0xF

RW

[4]

Completion Timeout disable

1

RW

UG-01097_sriov

2014.12.15

PCI Express Capability Structure

5-13

Registers

Altera Corporation