Altera Stratix V Avalon-ST User Manual

Page 89

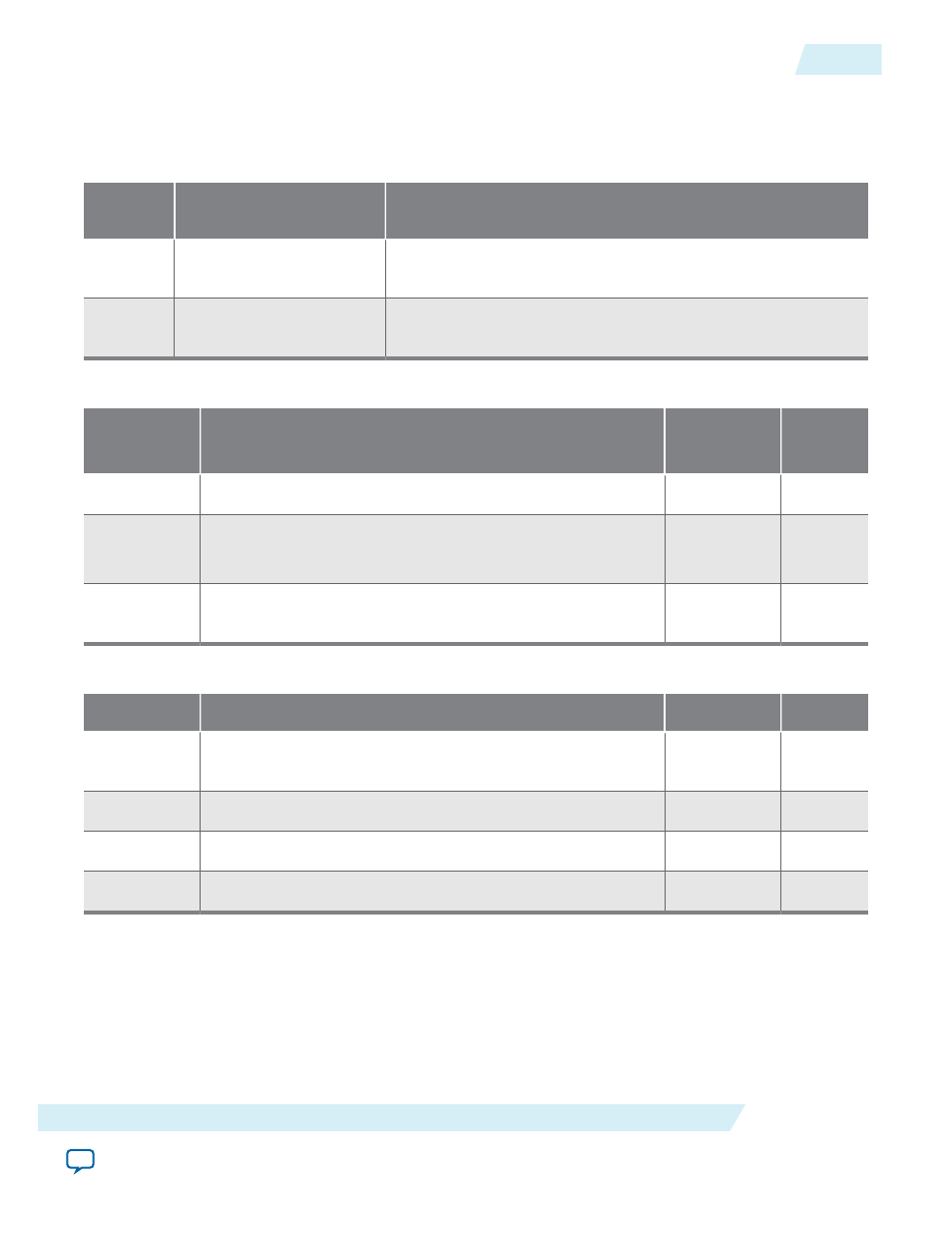

ARI Enhanced Capability Header and Control Register

Table 5-21: ARI Extended Capabilities Registers

Address

(hex)

Name

Description

0x100

ARI Enhanced Capability

Header

PCI Express Extended Capability ID for ARI and next capability

pointer.

0x104

ARI Capability Register, ARI

Control Register

The lower 16 bits implement the ARI Capability Register. The

upper 16 bits implement the ARI Control Register.

Table 5-22: ARI Enhanced Capability ID - 0x100

Bits

Register Description

Default Value

Default Value

Access

[15:0]

PCI Express Extended Capability ID.

0x000E

RO

[19:16]

Capability Version.

1

Default Value

RO

[31:20]

Next Capability Pointer: When ARI support is enabled, points to

AER Capability. Otherwise, points to NULL.

0x140

RO

Table 5-23: ARI Enhanced Capability Header and Control Register - 0x104

Bits

Register Description

Default Value

Access

[0]

Specifies support for arbitration at the Function group level. Not

implemented.

0

RO

[7:1]

Reserved.

0

RO

[15:8]

ARI Next Function Pointer. Pointer to the next PF.

1

RO

[31:61]

Reserved.

0

RO

UG-01097_sriov

2014.12.15

ARI Enhanced Capability Header and Control Register

5-15

Registers

Altera Corporation