Altera Stratix V Avalon-ST User Manual

Page 103

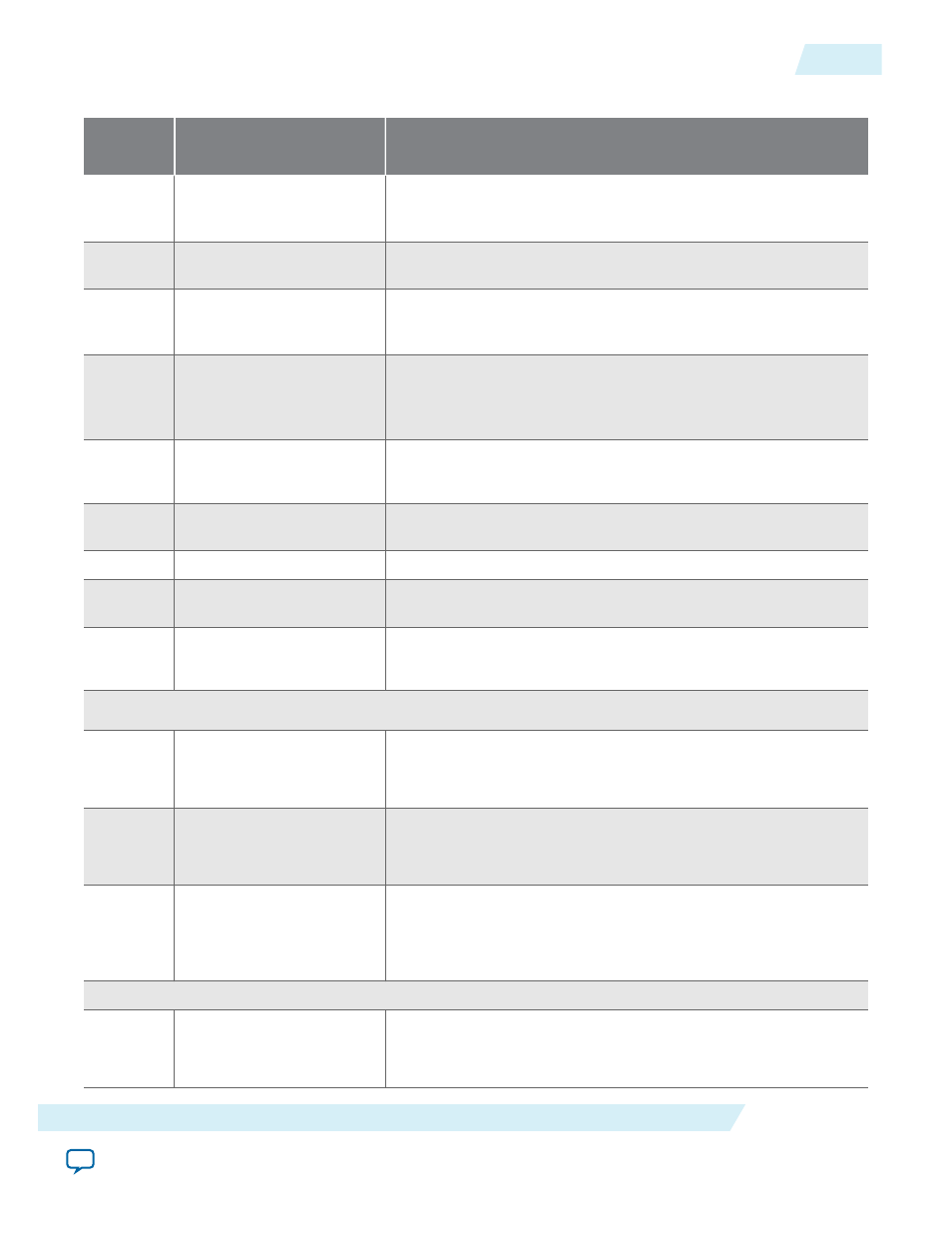

Table 5-46: Virtual Function Registers - Differences from PF

Address

(hex)

Name

Description

0x000

Vendor ID and Device ID

Register

Vendor ID Register and Device ID Registers defined in PCI

Express Base Specification 3.0 . These registers are hardwired to

all 1s.

0x004

Command and Status

Register

PCI Command and Status Registers. Refer to

for

descriptions of the implemented fields.

0x008

Revision ID and Class Code

Register

PCI Revision ID and Class Code Registers defined in PCI Express

Base Specification 3.0 . The VF has the same settings and access as

PF0.

0x00C

BIST, Header Type, Latency

Timer and Cache Line Size

Registers

Contains the following registers defined in the PCI Express Base

Specification 3.0 : BIST Register, Header Type Register, Latency

Timer, Cache Line Size Register. These registers are hardwired to

all 0s for VFs.

0x010:

0x028

Reserved

N/A

0x02C

Subsystem Vendor ID and

Subsystem ID Registers

PCI Subsystem Vendor ID and Subsystem ID Registers. The VF

has the same settings and access as PF0.

0x030

Reserved

N/A

0x034

Capabilities Pointer

This register points to the first Capability Structure in the PCI

Configuration Space. For VFs, it points to the MSI-X capability.

0x038:

0x03C

Reserved

N/A

MSI-X Capability Structure

0x068

MSI-X Control Register

Contains the MSI-X Message Control Register, Capability ID for

MSI-X, and the next capability pointer. The VF has the same

fields and access as the parent PF.

0x06C

MSI-X Table Offset

Points to the MSI-X Table in memory. Also specifies the BAR

corresponding to the memory segment where the MSI-X Table

resides. The VF has the same fields and access as the PF.

0x070

MSI-X PBA Offset

Points to the MSI-X Pending Bit Array in memory. Also,

specifies the BAR corresponding to the memory segment where

the PBA Array resides. The VF has the same fields and access as

the parent PF.

PCI Express Capability Structure

0x080

PCI Express Capability List

Register

Capability ID, PCI Express Capabilities Register, and the next

capability pointer. Refer to

for descriptions of the

implemented fields.

UG-01097_sriov

2014.12.15

Virtual Function Registers

5-29

Registers

Altera Corporation