Lmi signals, Hard ip for pcie – Altera Stratix V Avalon-ST User Manual

Page 57

Figure 4-8: MSI-X PBA Table

Pending Bits 0 through 63

Pending Bits 64 through 127

Pending Bits ((N - 1) div 64) × 64 through N - 1

QWORD 0

QWORD 1

QWORD (( N - 1) div 64)

Base

Address

Pending Bit Array (PBA)

Base + 1 × 8

Base + ((N - 1) div 64) × 8

4. The IRQ Processor reads the entry in the MSI-X table.

a. If the interrupt is masked by the

Vector_Control

field of the MSI-X table, the interrupt remains in

the pending state.

b. If the interrupt is not masked, IRQ Processor sends Memory Write Request to the TX slave

interface. It uses the address and data from the MSI-X table. If

Message Upper Address

= 0, the

IRQ Processor creates a three-dword header. If the

Message Upper Address > 0

, it creates a 4-

dword header.

5. The host interrupt service routine detects the TLP as an interrupt and services it.

Related Information

•

•

LMI Signals

LMI interface can write log error descriptor information in the TLP header log registers. The LMI access

to other registers is intended for debugging, not normal operation.

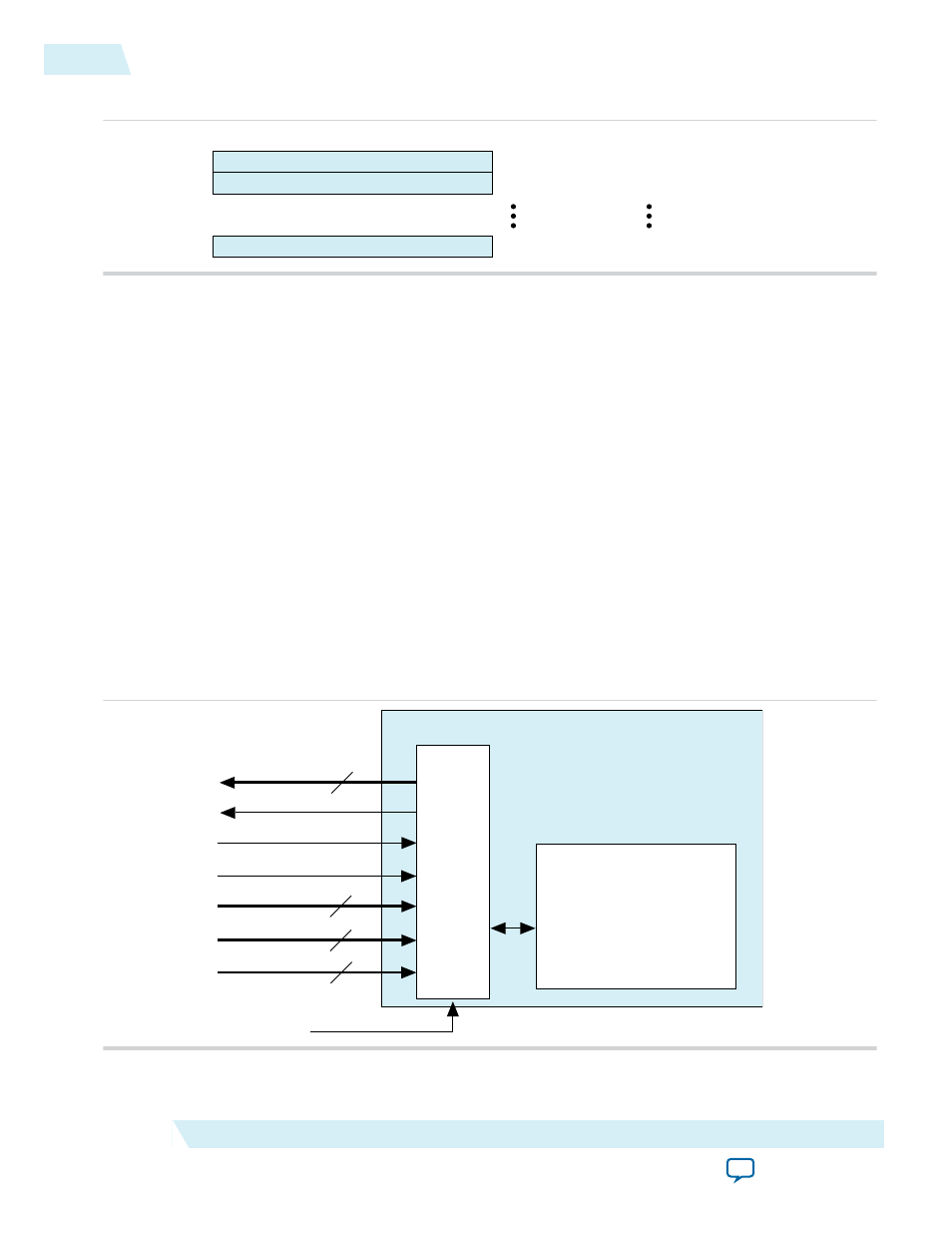

Figure 4-9: Local Management Interface

Configuration Space

128 32-bit registers

(4 KBytes)

LMI

32

lmi_dout

lmi_ack

12

lmi_addr

9

lmi_func

32

lmi_din

lmi_rden

lmi_wren

pld_clk

Hard IP for PCIe

4-22

LMI Signals

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions