Altera Stratix V Avalon-ST User Manual

Page 83

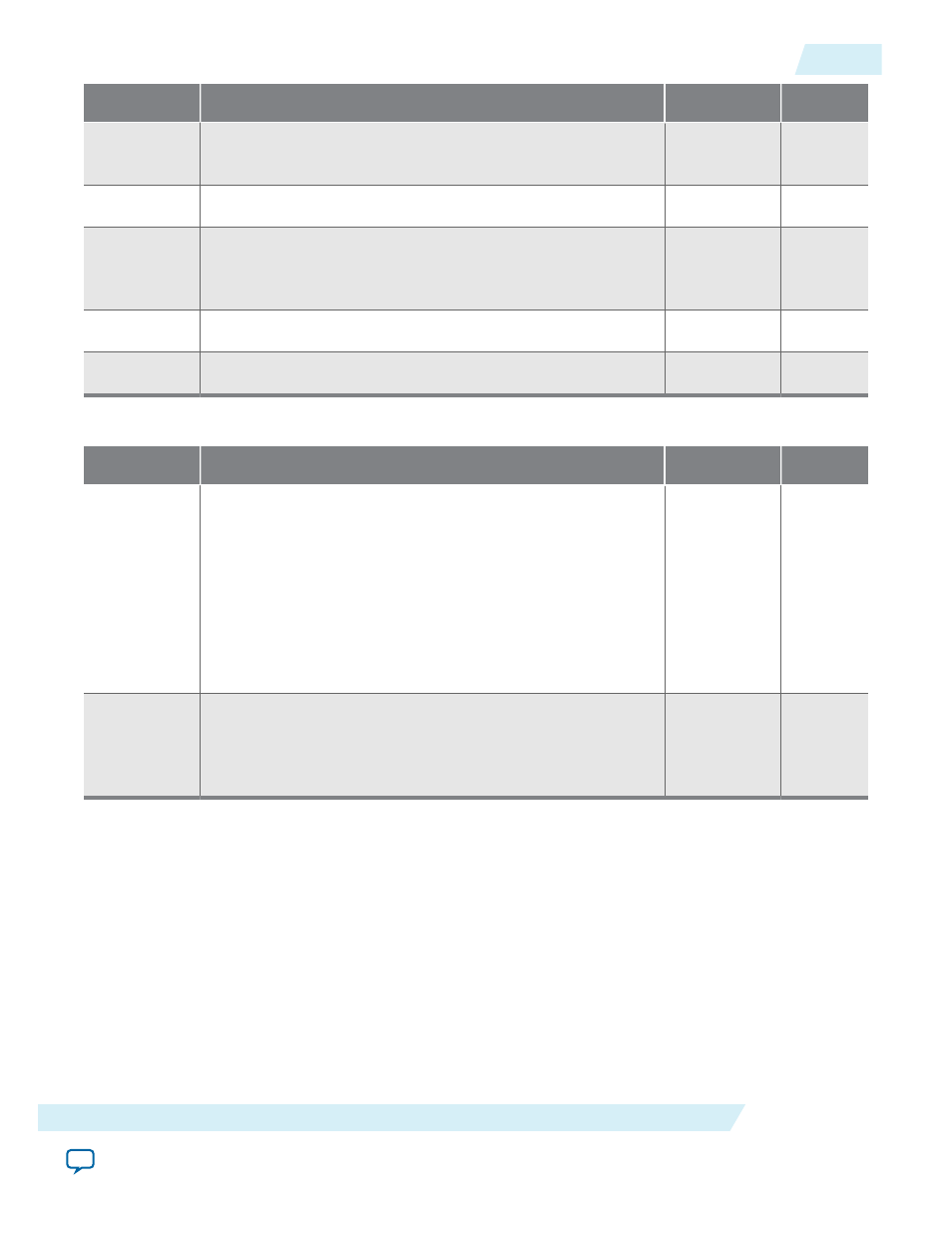

Bits

Register Description

Default Value

Access

[30]

MSI-X Function Mask. When set, masks all MSI-X interrupts

from this function.

0

RW

[29:27]

Reserved.

0

RO

[26:16 ]

Size of the MSI-X Table. The value in this field is 1 less than the

size of the table set up for this function. The maximum value is

0x7FF, or 4096 interrupt vectors.

Set in Qsys

RO

[15:8]

Next Capability Pointer. Points to Power Management Capability.

0x80

RO

[7:0]

Capability ID. PCI-SIG assigns this ID.

0x11

RO

Table 5-10: MSI-X Table Offset BAR Indicator Register - 0x06C

Bits

Register Description

Default Value

Access

[2:0]

MSI-X Table BAR Indicator. Specifies the BAR number whose

address range contains the MSI-X Table.

• 3'b000: BAR0

• 3'b001: BAR1

• 3'b010: BAR2

• 3'b011: BAR3

• 3'b100: BAR4

• 3'b101: BAR5

Set in Qsys

RO

[31:3]

Specifies the memory address offset for the MSI-X Table relative

to the BAR base address value of the BAR number specified in

MSI-X Table BAR Indicator,[2:0] above. The address is extended

by appending 3 zeroes to create quad-word alignment.

Set in Qsys

RO

UG-01097_sriov

2014.12.15

MSI-X Capability Structure

5-9

Registers

Altera Corporation