Sr-iov enhanced capability registers – Altera Stratix V Avalon-ST User Manual

Page 94

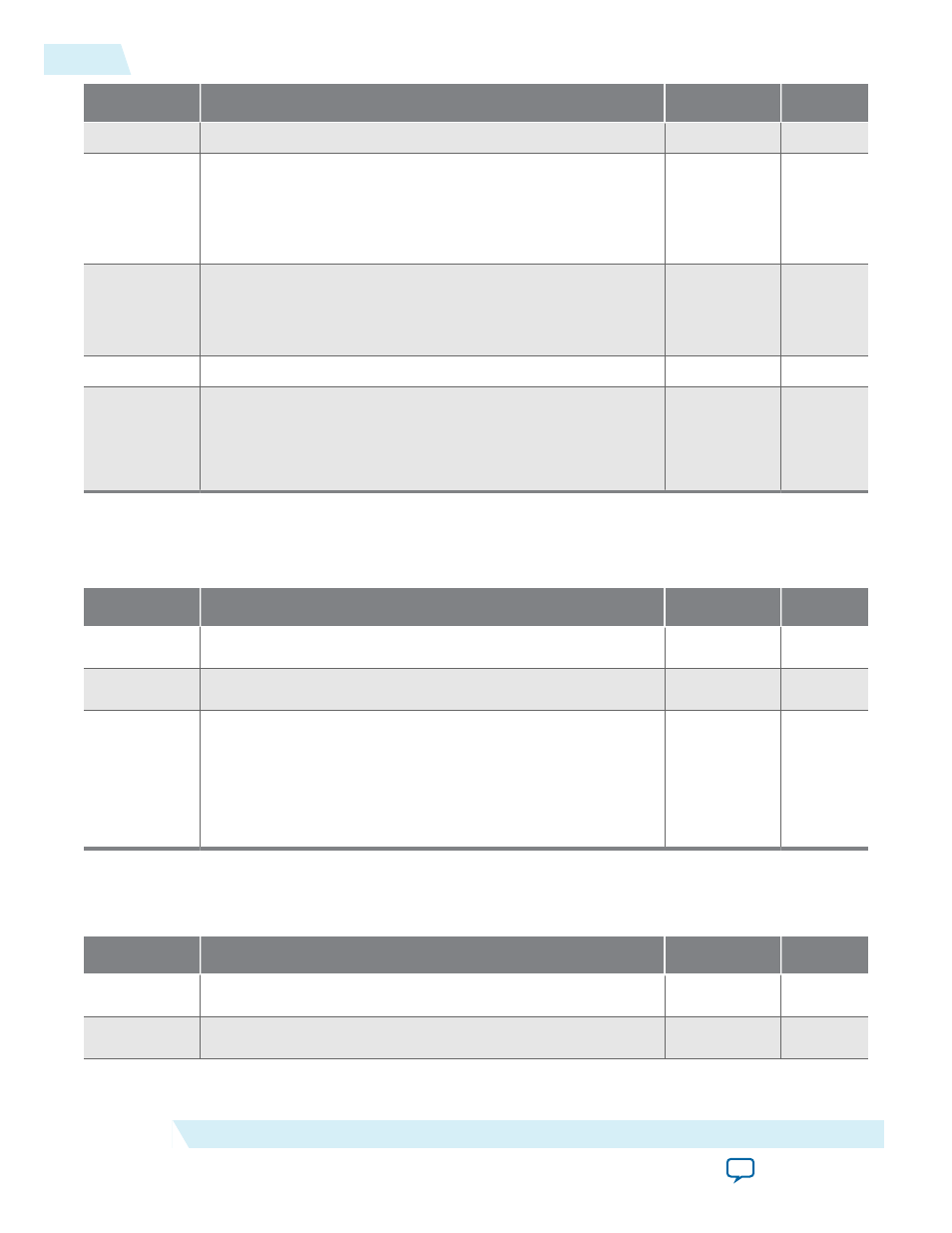

Bits

Register Description

Default Value

Access

[1]

Reserved. Hardwired to 0.

0

[2]

Specifies the BAR size.: The following encodings are defined:

• 1'b0: 32-bit BAR

• 1'b1: 64-bit BAR created by pairing BAR0 with BAR1, BAR2

with BAR3, or BAR4 with BAR5

0

RO

[3]

When 1, indicates that the data within the address range refined

by this BAR is prefetchable. When 1, indicates that the data is not

prefetchable. Data is prefetchable if reading is guaranteed not to

have side-effects .

Prefetchable: 0

Non-Prefetch‐

able: 1

RO

[7:4]

Reserved. Hardwired to 0.

0

RO

[31:8]

Base address of the BAR. The number of writeable bits is based on

the BAR access size. For example, if bits [15:8] are hardwired to 0,

if the BAR access size is 64 Kbytes. Bits [31:16] can be read and

written.

0

See

description

SR-IOV Enhanced Capability Registers

Table 5-28: SR-IOV Enhanced Capability Header Register - 0x180

Bits

Register Description

Default Value

Access

[15:0]

PCI Express Extended Capability ID

0x0010

RO

[19:16]

Capability Version

1

RO

[31:16]

Next Capability Pointer: The value depends on data rate. The

following values are possible:

• If PF0 supports the Gen3 data rate: Next Capability =

Secondary PCIe (0x200).

• Else: Next Capability = 0.

Set in Qsys

RO

Default Value

Table 5-29: SR-IOV Capabilities Register - 0x184

Bits

Register Description

Default Value

Access

[0]

VF Migration Capable

0

RO

[1]

ARI Capable Hierarchy Preserved

1

RO

5-20

SR-IOV Enhanced Capability Registers

UG-01097_sriov

2014.12.15

Altera Corporation

Registers