Pipe interface signals – Altera Stratix V Avalon-ST User Manual

Page 71

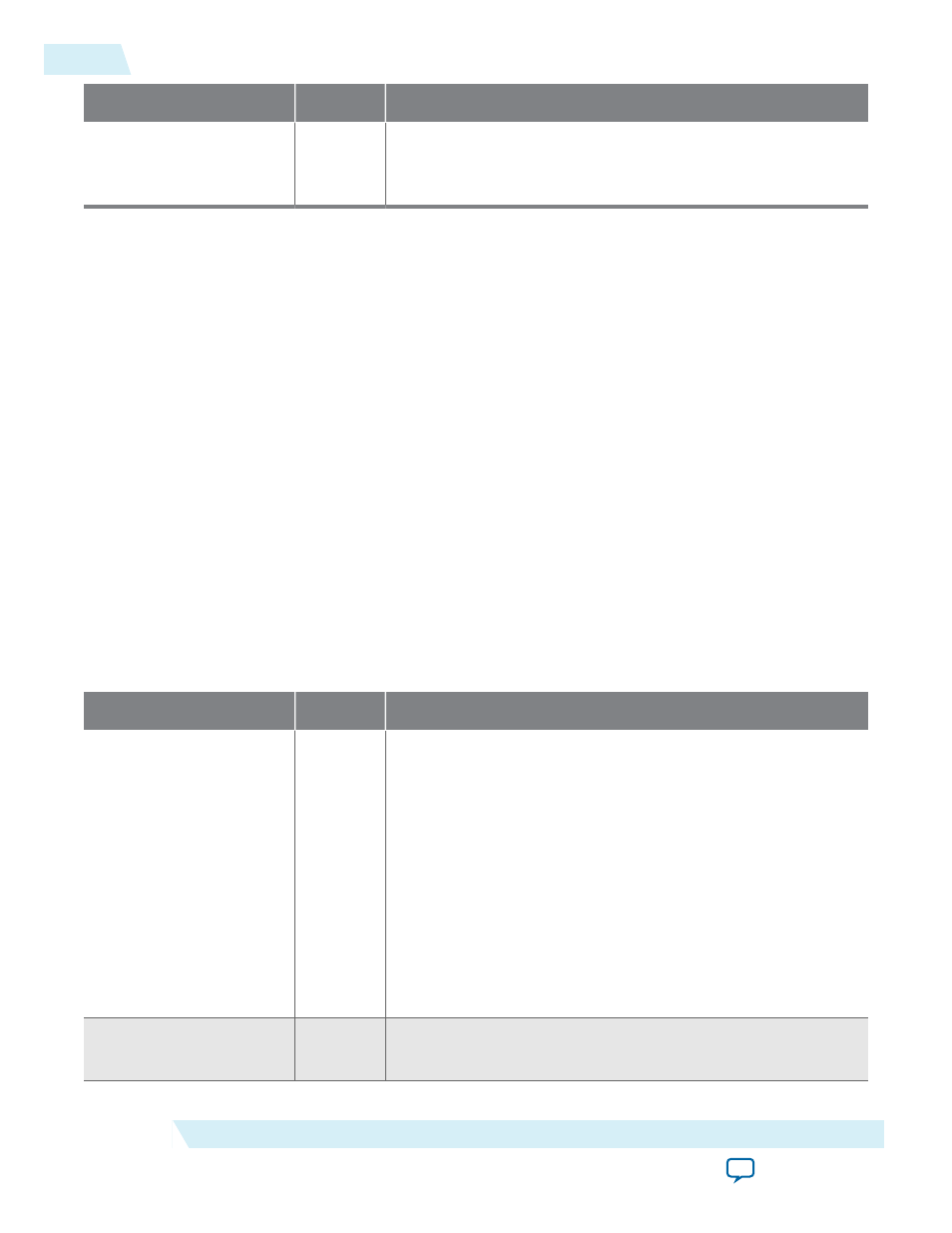

Signal

Direction

Description

hpg_ctrler[4:0]

Input

This signal is only available in Root Port mode and when the Slot

capability register is enabled. For Endpoint variations the

hpg_

ctrler

input should be hardwired to 0s.

Related Information

PIPE Interface Signals

These PIPE signals are available for Gen1, Gen2, and Gen3 variants so that you can simulate using either

the serial or the PIPE interface. Simulation is faster using the PIPE interface because the PIPE simulation

bypasses the serdes model. By default, the PIPE interface is 8 bits for Gen1 and Gen2 and 32 bits for Gen3.

You can use the PIPE interface for simulation even though your actual design includes a serial interface to

the internal transceivers. However, it is not possible to use the Hard IP PIPE interface in hardware,

including probing these signals using SignalTap

®

II Embedded Logic Analyzer. These signals are not top-

level signals of the Hard IP. They are listed here to assist in debugging link training issues.

Note: The Altera Root Port BFM bypasses Gen3 Phase 2 and Phase 3 Equalization. However, Gen3

variants can perform Phase 2 and Phase 3 equalization if instructed by a third-party BFM.

Table 4-19: PIPE Interface Signals

In the following table, signals that include lane number 0 also exist for lanes 1-7. These signals are for simulation

only. For Quartus II software compilation, these pipe signals can be left floating. In Qsys, the signals that are part

of the PIPE interface have the prefix, hip_pipe. The signals which are included to simulate the PIPE interface have

the prefix, hip_pipe_sim_pipe

Signal

Direction

Description

eidleinfersel0[2:0]

Output

Electrical idle entry inference mechanism selection. The

following encodings are defined:

• 3'b0xx: Electrical Idle Inference not required in current

LTSSM state

• 3'b100: Absence of COM/SKP Ordered Set the in 128 us

window for Gen1 or Gen2

• 3'b101: Absence of TS1/TS2 Ordered Set in a 1280 UI interval

for Gen1 or Gen2

• 3'b110: Absence of Electrical Idle Exit in 2000 UI interval for

Gen1 and 16000 UI interval for Gen2

• 3'b111: Absence of Electrical idle exit in 128 us window for

Gen1

phystatus0

Input

PHY status <n>. This signal communicates completion of several

PHY requests.

4-36

PIPE Interface Signals

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions