Clock signals, Function-level reset interface – Altera Stratix V Avalon-ST User Manual

Page 48

Signal

Directi

on

Description

ko_cpl_spc_

header]7:0]

Output The Application Layer can use this signal to build circuitry to prevent RX

buffer overflow for completion headers. Endpoints must advertise infinite

space for completion headers; however, RX buffer space is finite.

ko_cpl_

spc_header

is a static signal that indicates the total number of completion

headers that can be stored in the RX buffer.

Related Information

Clock Signals

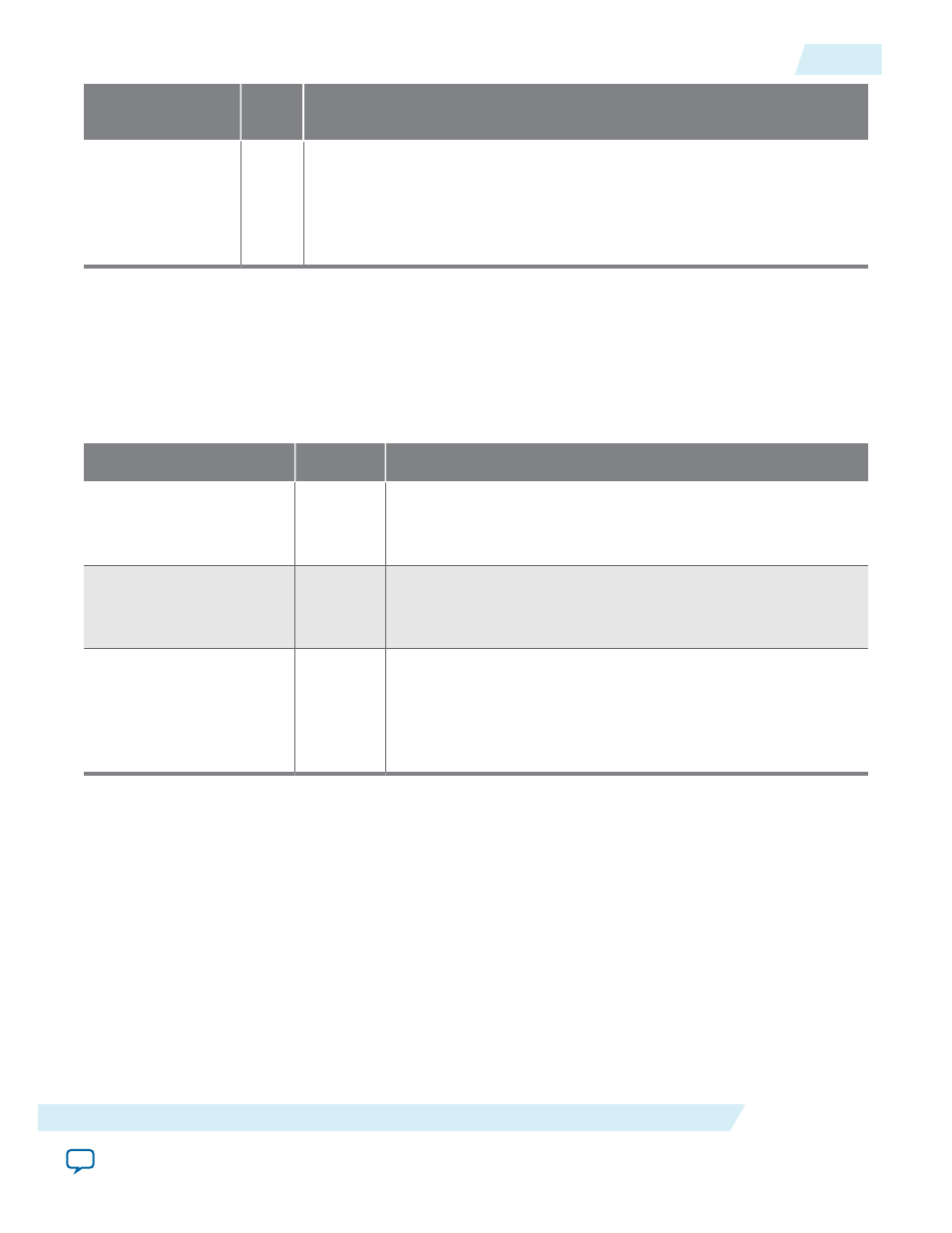

Table 4-6: Clock Signals Hard IP Implementation

Signal

Direction

Description

refclk

Input

Reference clock for the Stratix V Hard IP for PCI Express. It

must have the frequency specified under the System Settings

heading in the parameter editor.

pld_clk

Input

Clocks the Application Layer. You can drive this clock with

coreclkout_hip

. If you drive

pld_clk

with another clock

source, it must be equal to or faster than

coreclkout

.

coreclkout

Output

This is a fixed frequency clock used by the Data Link and

Transaction Layers. To meet PCI Express link bandwidth

constraints, this clock has minimum frequency requirements as

listed in coreclkout_hip Values for All Parameterizations in the

Reset and Clocks chapter .

Refer to Stratix V Hard IP for PCI Express Clock Domains in the Reset and Clocks chapter for more

information about clocks.

Function-Level Reset Interface

The function-level reset (FLR) interface can reset the individual SR-IOV functions.

UG-01097_sriov

2014.12.15

Clock Signals

4-13

Interfaces and Signal Descriptions

Altera Corporation