Altera Stratix V Avalon-ST User Manual

Page 81

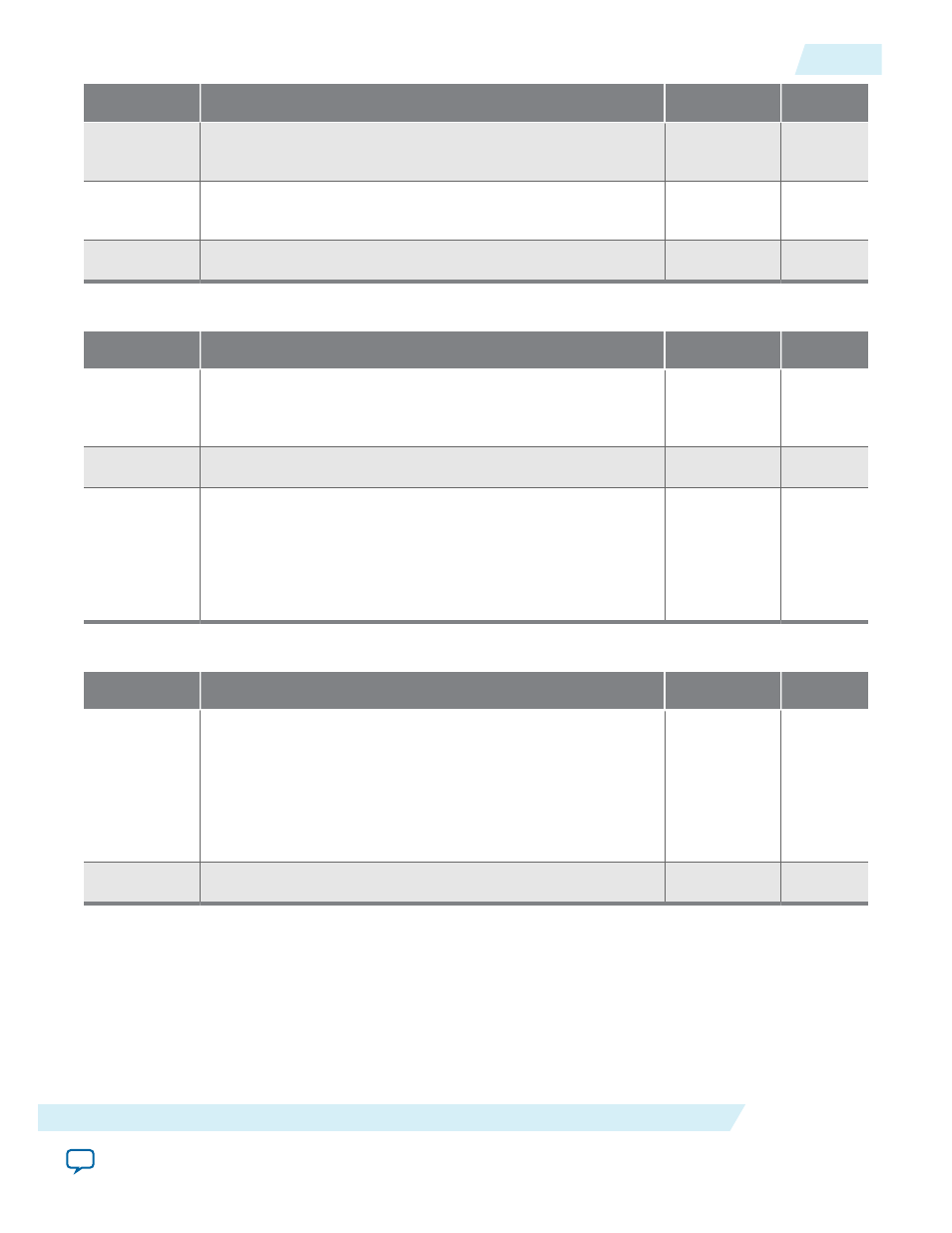

Bits

Register Description

Default Value

Access

[16]

MSI Enable. This bit must be set to enable the MSI interrupt

generation.

0

RW

[15:8]

Next Capability Pointer. Points to either MSI-X or Power

Management Capability.

0x68 or 0x78

RO

[7:0]

Capability ID. PCI-SIG assigns this value.

0x05

RO

Table 5-5: MSI Message Address Registers - 0x054 and 0x058

Bits

Register Description

Default Value

Access

[1:0]

The two least significant bits of the memory address. These are

hardwired to 0 to align the memory address on a Dword

boundary.

0

RO

[31:2]

Lower address for the MSI interrupt.

0

RW

[31:0]

Upper 32 bits of the 64-bit address to be used for the MSI

interrupt. If the

64-bit Addressing Capable

bit in the

MSI

Control

register is set to 1, this value is concatenated with the

lower 32-bits to form the memory address for the MSI interrupt.

When the

64-bit Addressing Capable

bit is 0, this register

always reads as 0.

0

RW

Table 5-6: MSI Message Data Register - 0x058 (32-bit addressing) or 0x05C (64-bit addressing) Register

Bits

Register Description

Default Value

Access

[15:0]

Data for MSI Interrupts generated by this function. This base

value is written to Root Port memory to signal an MSI interrupt.

When one MSI vector is allowed, this value is used directly. When

2 MSI vectors are allowed, the upper 15 bits are used. And, the

least significant bit indicates the interrupt number. When 4 MSI

vectors are allowed, the lower 2 bits indicate the interrupt

number, and so on.

0

RW

[31:16

Reserved

0

RO

UG-01097_sriov

2014.12.15

MSI Registers

5-7

Registers

Altera Corporation