Reset, status, and link training signals – Altera Stratix V Avalon-ST User Manual

Page 59

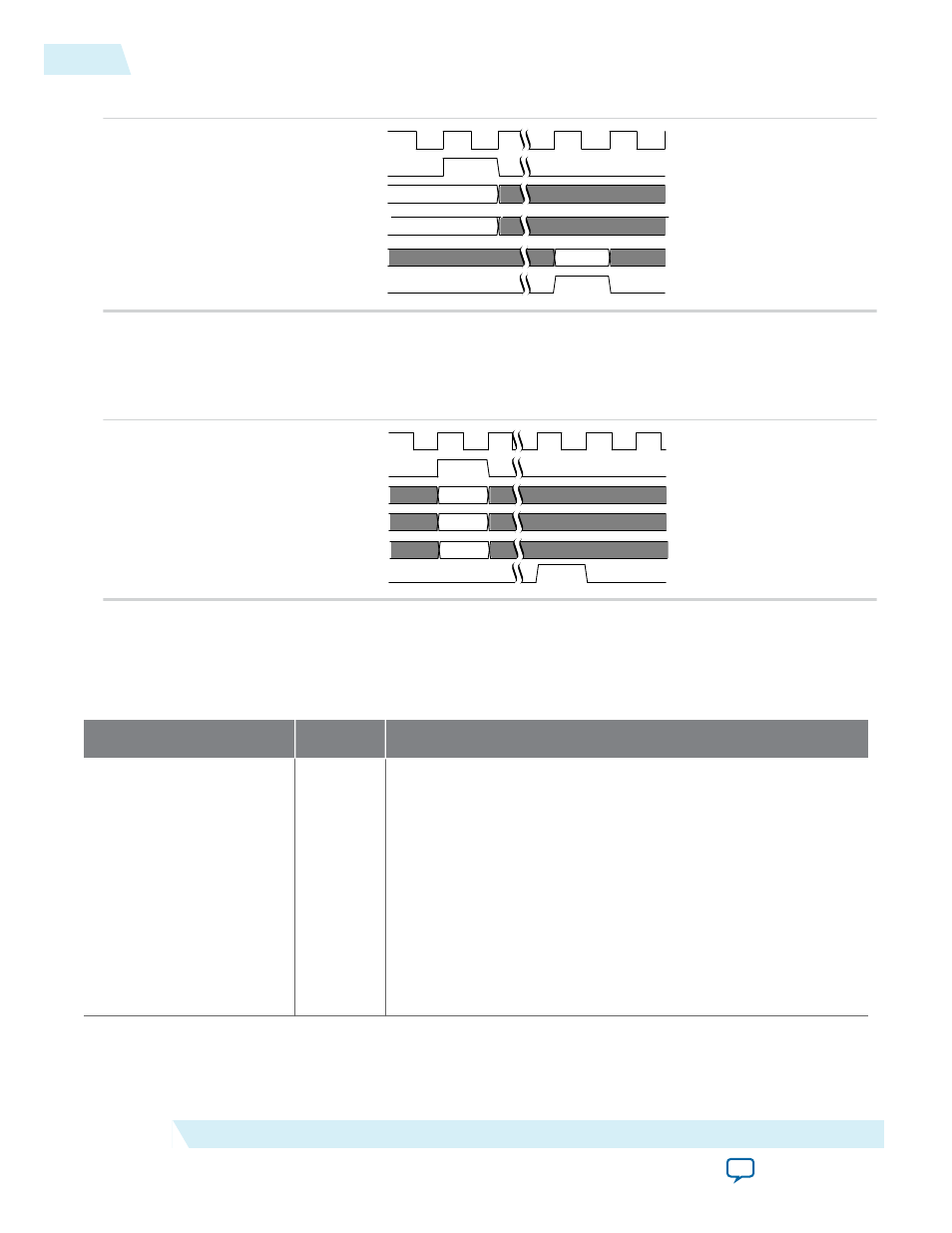

Figure 4-10: LMI Read

pld_clk

lmi_rden

lmi_addr[11:0]

lmi_dout[31:0]

lmi_ack

lmi_addr[8:0]

Figure 4-11: LMI Write

The following figure illustrates the LMI write. Only writeable configuration bits are overwritten by this

operation. Read-only bits are not affected. LMI write operations are not recommended for use during

normal operation with the exception of AER header logging.

pld_clk

lmi_wren

lmi_din[31:0]

lmi_addr[11:0]

lmi_ack

lmi_func[8:0]

Reset, Status, and Link Training Signals

Table 4-12: Reset Signals

Signal

Direction

Description

npor

Input

Active low reset signal. In the Altera hardware example designs,

npor

is the

OR

of

pin_perst

and

local_rstn

coming from the

software Application Layer. If you do not drive a soft reset signal

from the Application Layer, this signal must be derived from

pin_perst

. You cannot disable this signal. Resets the entire

Stratix V Hard IP for PCI Express IP Core and transceiver.

Asynchronous.

In systems that use the hard reset controller, this signal is edge,

not level sensitive; consequently, you cannot use a low value on

this signal to hold custom logic in reset. For more information

about the hard and soft reset controllers, refer to Reset.

4-24

Reset, Status, and Link Training Signals

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions