Refer to, Figure 4-2, Below – Altera Stratix V Avalon-ST User Manual

Page 52: Is high. refer to

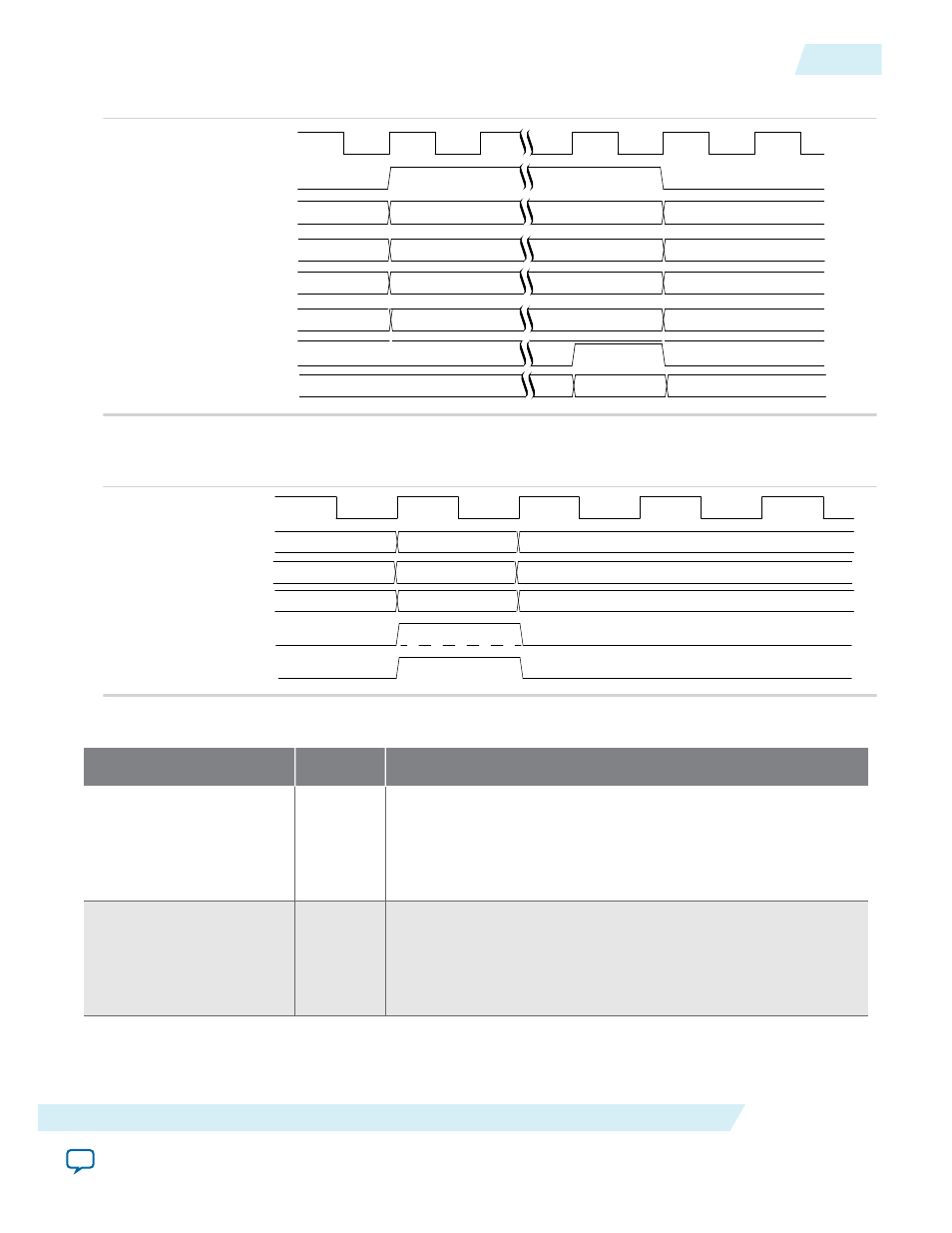

Figure 4-1: Timing Diagram for MSI Interrupt Generation

pld_clk

MSI Function No

MSI Number

Status

MSI TC

app_msi_req

app_msi_req_fn[7:0]

app_msi_num[4:0]

app_msi_tc[2:0]

app_msi_ack

MSI Data

app_msi_data_pf[15:0]

app_msi_status[1:0]

Figure 4-2: Timing Diagram for MSI Pending Bit Write Operation

The MSI Pending Bit Write Operation aborts the pending MSI interrupt.

pld_clk

app_msi_req_fn[7:0]

MSI Function No.

MSI Data

app_msi_pending_bit_wr_data

app_msi_pending_bit_wr_en

MSI Vector

app_msi_num[4:0]

app_msi_data_pf[15:0]

Table 4-9: MSI-X Interrupts

Signal

Direction

Description

app_msix_req

Input

When asserted, the Application Layer is requesting that an MSI-

X interrupt be sent. Assertion causes an MSI-X posted write TLP

to be generated. The MSI-X TLP uses data from

app_msi_req_

fn

,

app_msix_addr

,

app_msix_data

, and

app_msi_tc

inputs.

Refer to

below.

app_msix_ack

Output

Ack for MSI-X interrupts. When asserted, indicates that Hard IP

has sent an MSI-X posted write TLP in response

app_msix_req

.

The Application Layer must wait for after asserting

app_msix_

req

. The Application Layer must de-assert

app_msix_req

for at

least 1 cycle before signaling a new MSI interrupt.

UG-01097_sriov

2014.12.15

Interrupt Interface

4-17

Interfaces and Signal Descriptions

Altera Corporation