Top-level interfaces, Clocks and reset, Transceiver reconfiguration – Altera Stratix V Avalon-ST User Manual

Page 126

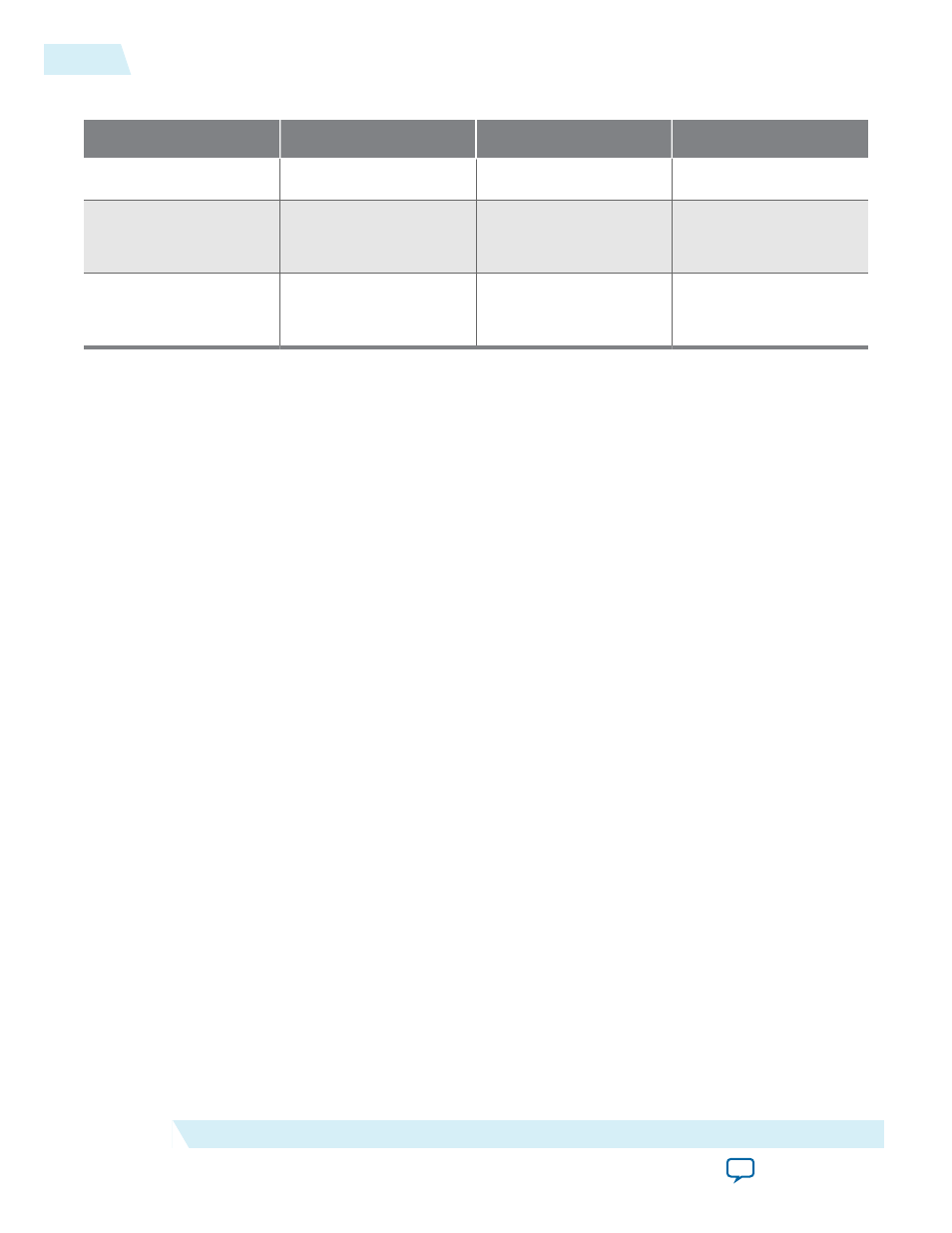

Table 9-1: Application Layer Clock Frequencies

Lanes

Gen1

Gen2

Gen3

×2

N/A

N/A

125 MHz @ 128 bits

×4

N/A

125 MHz @ 128 bits

250 MHz @ 128 bits or

125 MHz @ 256 bits

×8

125 MHz @ 128 bits

250 MHz @ 128 bits or

125 MHz @ 256 bits

250 MHz @ 256 bits

Related Information

Top-Level Interfaces

Clocks and Reset

The PCI Express Base Specification requires an input reference clock, which is called

refclk

in this design.

The PCI Express Base Specification stipulates that the frequency of this clock be 100 MHz.

The PCI Express Base Specification also requires a system configuration time of 100 ms. To meet this

specification, IP core includes an embedded hard reset controller. This reset controller exits the reset state

after the I/O ring of the device is initialized.

Related Information

Reset, Status, and Link Training Signals

Transceiver Reconfiguration

The transceiver reconfiguration interface allows you to dynamically reconfigure the values of analog

settings in the PMA block of the transceiver. Dynamic reconfiguration is necessary to compensate for

process variations.

Related Information

Transceiver PHY IP Reconfiguration

on page 11-1

9-2

Top-Level Interfaces

UG-01097_sriov

2014.12.15

Altera Corporation

IP Core Architecture