Completion side band signals – Altera Stratix V Avalon-ST User Manual

Page 45

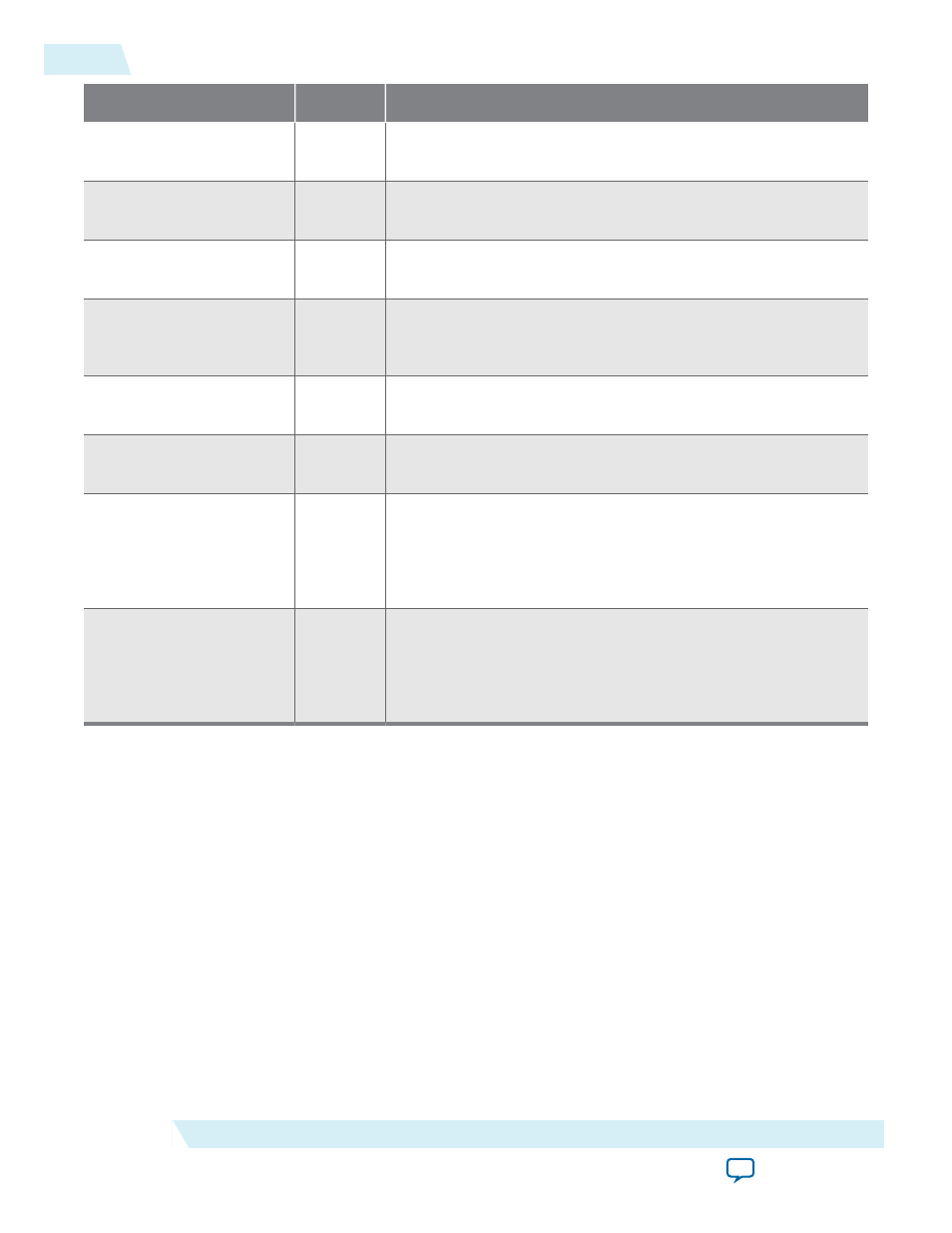

Signal

Direction

Description

mem_space_en_pf[<n>-

1:0]

Output

The PF0 and PF1 PCI Command Registers drive the Memory

Space Enable bit.

bus_master_en_pf[<n>-

1:0]

Output

ThePF0 and PF1 PCI Command Registers drive the Bus Master

Enable bit .

mem_space_en_vf[<n>-

1:0]

Output

The PF0 and PF1 Control Registers drive the SR-IOV Memory

Space Enable bit.

bus_master_en_vf[<n>-

1:0]

Output

The VF<n> Memory Space Enable bit of the PCI Command

Register drives bit <n> of this bus. <n> is the total number of

VFs.

Pf0_num_vfs[7:0]

Output

This output drives the value of the

NumVFs

register in the PF0 SR-

IOV Capability Structure.

Pf1_num_vfs[7:0]

Output

This output drives the value of the

NumVFs

register in the PF1 SR-

IOV Capability Structure .

max_payload_size[2:0]

Output

When only PF0 is present, the max payload size field of the PF0

PCI Express Device Control Register drives this output. When

two PFs are present, the minimum value of the max payload size

field of the PCI Express Device Control Registers drives this

output.

rd_req_size[2:0]

Output

When only PF 0 is present, the max read request size field of PF0

PCI Express Device Control Register drives this output. When

two PFs are present, the minimum value of the max read request

size fields of the PCI Express Device Control Registers drives this

output.

Completion Side Band Signals

The following table describes the signals that comprise the completion side band signals for the Avalon-

ST interface. The Stratix V Hard IP for PCI Express provides a completion error interface that the

Application Layer can use to report errors, such as programming model errors. When the Application

Layer detects an error, it can assert the appropriate

cpl_err

bit to indicate what kind of error to log. If

separate requests result in two errors, both are logged. The Hard IP sets the appropriate status bits for the

errors in the Configuration Space, and automatically sends error messages in accordance with the PCI

Express Base Specification. Note that the Application Layer is responsible for sending the completion with

the appropriate completion status value for non-posted requests. Refer to

on page 8-1

for information on errors that are automatically detected and handled by the Hard IP.

For a description of the completion rules, the completion header format, and completion status field

values, refer to Section 2.2.9 of the PCI Express Base Specification.

4-10

Completion Side Band Signals

UG-01097_sriov

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions