Axi4-lite write transaction master and slave roles, Figure 1-1. execute write transaction – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

Page 23

Mentor VIP Altera Edition

AXI4-Lite Transactions

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

23

April 2014

and *READY, that indicates valid information on a channel and the acceptance of the

information from the channel.

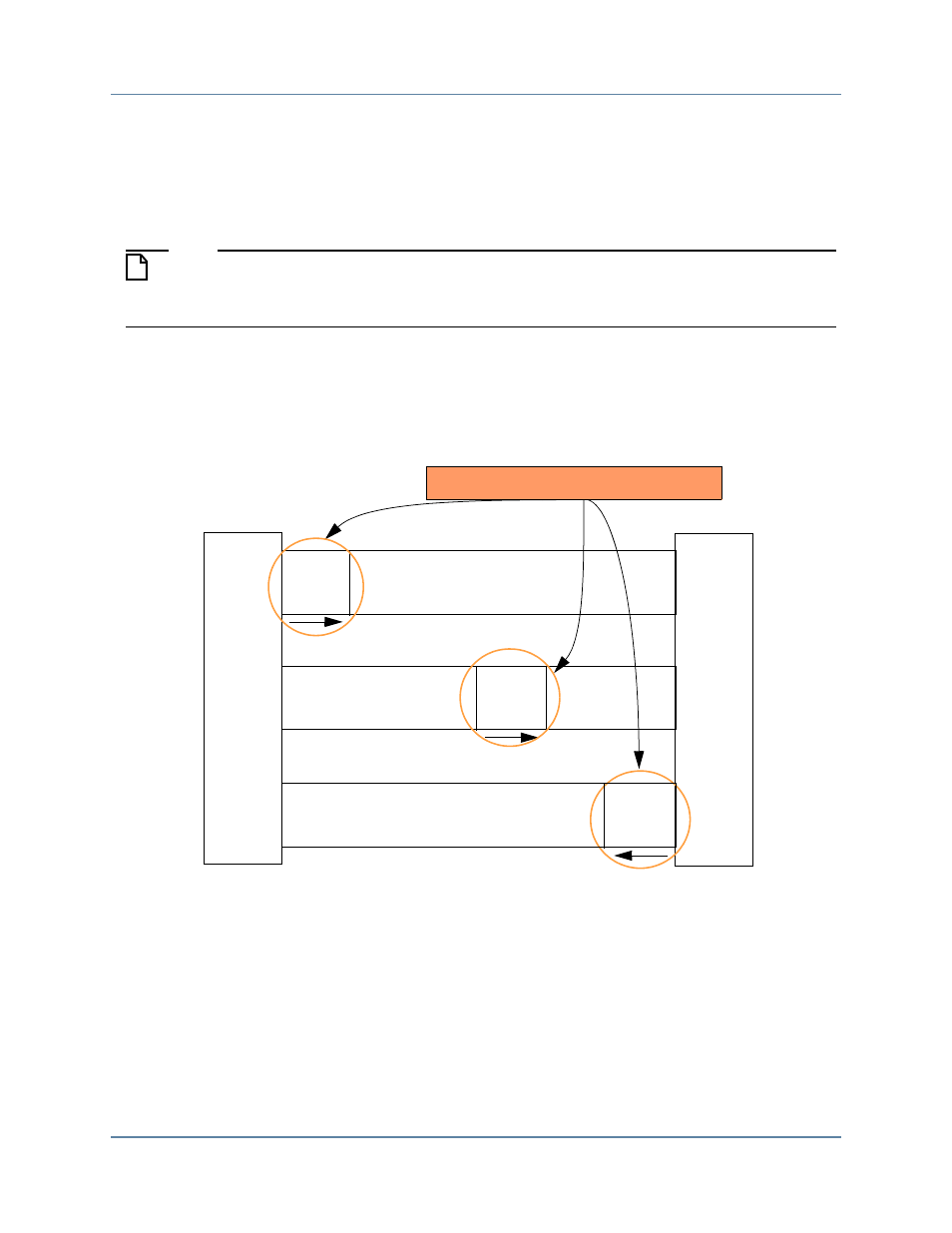

AXI4-Lite Write Transaction Master and Slave Roles

Note

The following description of a write transaction references SystemVerilog BFM API

tasks. There are equivalent VHDL BFM API procedures that perform the same

functionality.

For a write transaction, the master calls the

task to define the

information to be transferred and then calls the

task to initiate the transfer

of information as

illustrates.

Figure 1-1. Execute Write Transaction

task results in the master calling the

Master

interface

Slave

interface

Write

data

Write response channel

Write data channel

Write address channel

Write

response

Address

and

control

execute_transaction(t)