Verifying a master dut – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

Page 340

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

340

VHDL Tutorials

Verifying a Master DUT

April 2014

variable. The whole process runs concurrently with other

processes in the test program, using the path_id = AXI4_PATH_6. See “

” on page 151 for details of path_id, and is similar in operation to the

AXI4-Lite VHDL Master BFM Test Program

on page 397 for the complete handle_read_data_ready code listing.

Verifying a Master DUT

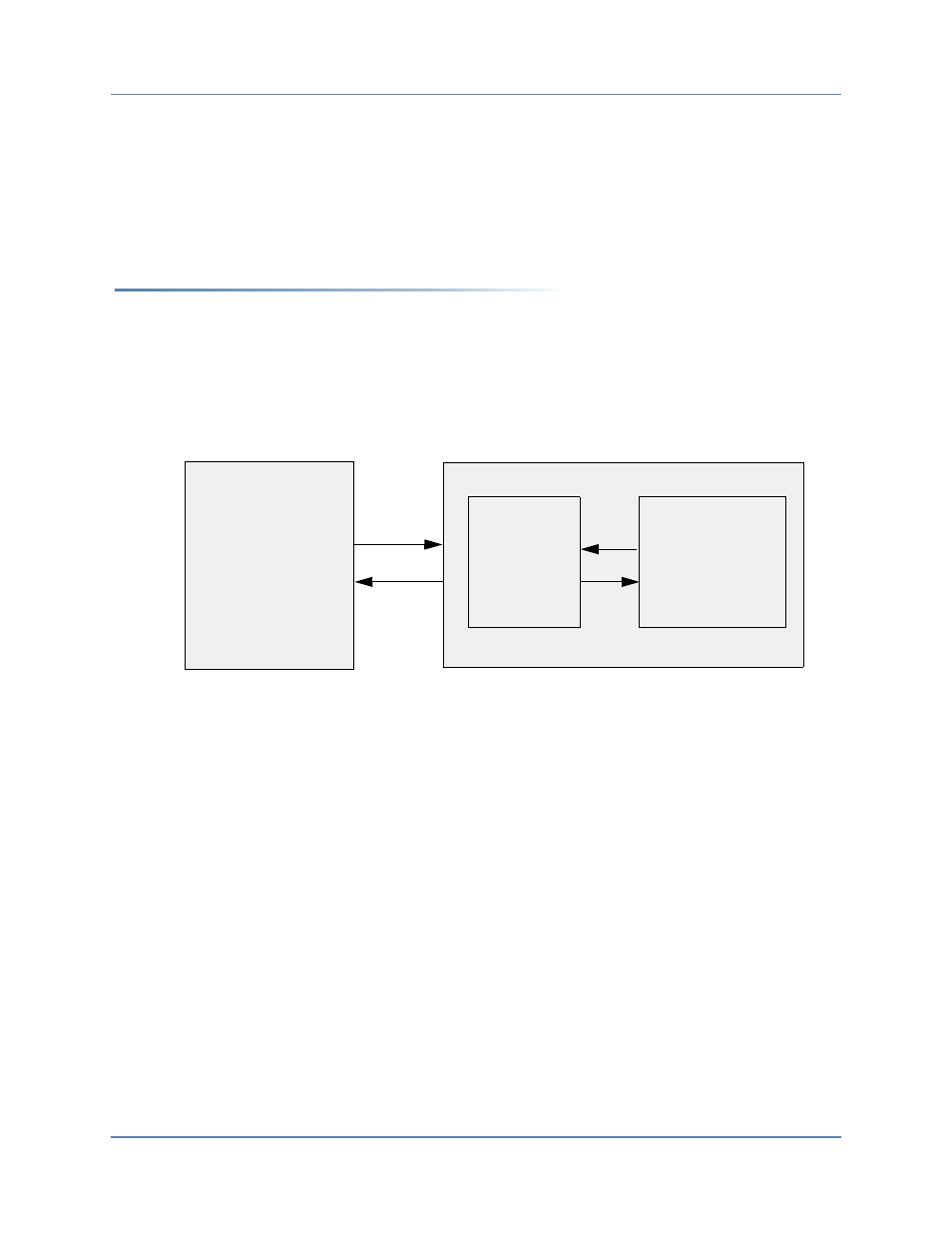

A master DUT component is connected to a slave BFM at the signal-level. A slave test program,

written at the transaction-level, generates stimulus via the slave BFM to verify the master DUT.

illustrates a typical top-level test bench environment.

Figure 11-2. Master DUT Top-Level Test Bench Environment

In this example, the slave test program is a simple memory model.

A top-level file instantiates and connects all the components required to test and monitor the

DUT, and controls the system clock (ACLK) and reset (ARESETn) signals.

Slave

BFM

Master

DUT

Slave test program

Top-level file