Table 42: rgmii interface signals, Figure 35: rgmii interface signals – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 100

Ethernet Interface

III-88

Slave Controller

– IP Core for Xilinx FPGAs

EtherCAT

device

nRGMII_LINK

CLK25_2NS

RGMII_RX_CLK

RGMII_RX_CTL_DATA_DDR_NRESET

RGMII_RX_CTL_DATA_DDR_CLK

RGMII_RX_CTL_DDR_L

RGMII_RX_CTL_DDR_H

NPHY_RESET_OUT

RGMII_RX_DATA_DDR_L[3:0]

RGMII_RX_DATA_DDR_H[3:0]

RGMII_TX_CLK_DDR_NRESET

RGMII_TX_CLK_DDR_CLK

RGMII_TX_CLK_DDR_L

RGMII_TX_CLK_DDR_H

RGMII_TX_CTL_DATA_DDR_NRESET

RGMII_TX_CTL_DATA_DDR_CLK

RGMII_TX_CTL_DDR_L

RGMII_TX_CTL_DDR_H

RGMII_TX_DATA_DDR_L[3:0]

RGMII_TX_DATA_DDR_H[3:0]

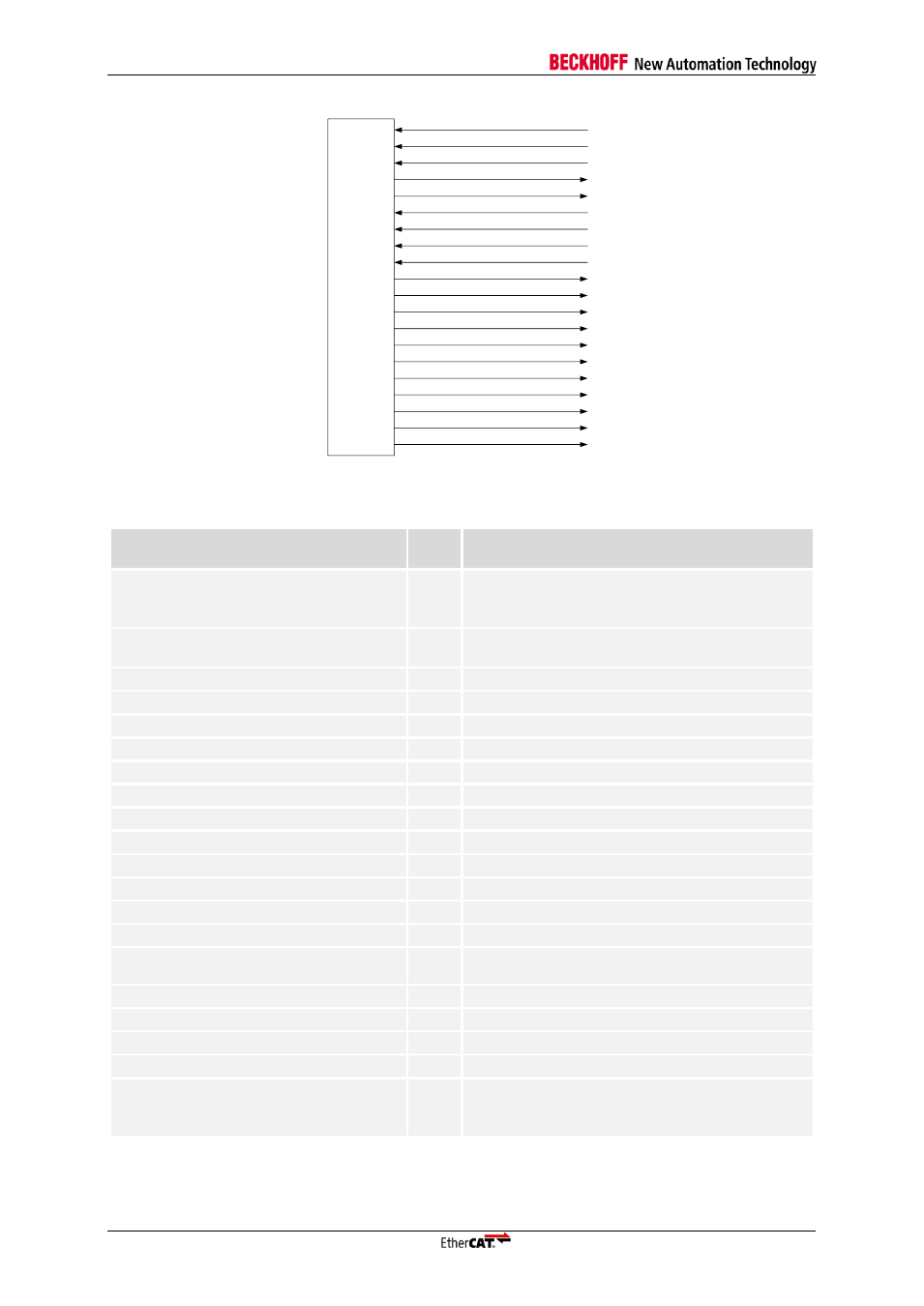

Figure 35: RGMII Interface signals

Table 42: RGMII Interface signals

Signal

Dire

ction

Description

CLK25_2NS

IN

25 MHz clock signal from PLL (rising edge 2 ns

after rising edge of CLK25), used for RGMII

GTX_CLK

nRGMII_LINK

IN

Input signal provided by the PHY if a 100 Mbit/s

(Full Duplex) link is established (alias LINK_MII)

RGMII_RX_CLK

IN

Receive clock

RGMII_RX_CTL_DATA_DDR_CLK

OUT

Receive control/data DDR input clock

RGMII_RX_CTL_DATA_DDR_NRESET

OUT

Receive control/data DDR input reset (act. low)

RGMII_RX_CTL_DDR_L

IN

Receive control DDR input low

RGMII_RX_CTL_DDR_H

IN

Receive control DDR input high

RGMII_RX_DATA_DDR_L[3:0]

IN

Receive data DDR input low

RGMII_RX_DATA_DDR_H[3:0]

IN

Receive data DDR input high

RGMII_TX_CLK_DDR_CLK

OUT

Transmit clock DDR output clock

RGMII_TX_CLK_DDR_NRESET

OUT

Transmit clock DDR output reset (act. low)

RGMII_TX_CLK_DDR_L

OUT

Transmit clock DDR output low

RGMII_TX_CLK_DDR_H

OUT

Transmit clock DDR output high

RGMII_TX_CTL_DATA_DDR_CLK

OUT

Transmit control/data DDR output clock

RGMII_TX_CTL_DATA_DDR_NRESET

OUT

Transmit control/data DDR output reset (act.

low)

RGMII_TX_CTL_DDR_L

OUT

Transmit control DDR output low

RGMII_TX_CTL_DDR_H

OUT

Transmit control DDR output high

RGMII_TX_DATA_DDR_L[3:0]

OUT

Transmit data DDR output low

RGMII_TX_DATA_DDR_H[3:0]

OUT

Transmit data DDR output high

NPHY_RESET_OUT

OUT

PHY reset (akt. low), resets PHY while ESC is in

Reset state, and, for FX PHYs, if Enhanced Link

Detection detects a lost link

NOTE: A pull-down resistor is typically required for NPHY_RESET_OUT to hold the PHY in reset state while the

FPGA is configured, since this pin is floating or even pulled up during that time.