1 mii interface, Mii interface, Table 23: phy interface mii – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 76

IP Core Signals

III-64

Slave Controller

– IP Core for Xilinx FPGAs

8.5.1

MII Interface

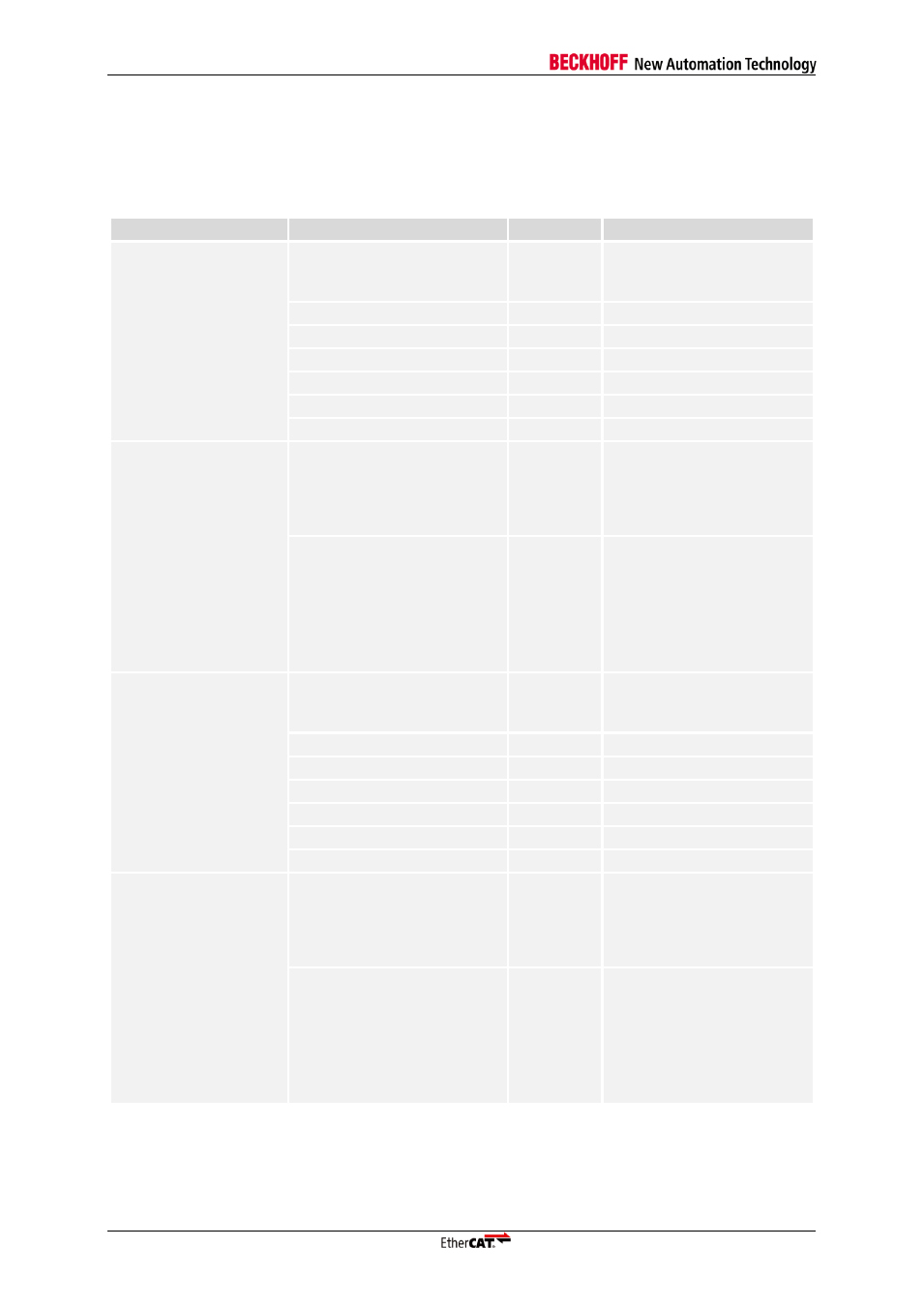

Table 23 lists the signals used with MII. The TX_CLK signals of the PHYs are not connected to the IP

Core unless TX Shift automatic configuration is enabled.

Table 23: PHY Interface MII

Condition

Name

Direction

Description

Port0 = MII

nMII_LINK0

INPUT

0: 100 Mbit/s (Full

Duplex) link at port 0

1: no link at port 0

MII_RX_CLK0

INPUT

Receive clock port 0

MII_RX_DV0

INPUT

Receive data valid port 0

MII_RX_DATA0[3:0]

INPUT

Receive data port 0

MII_RX_ERR0

INPUT

Receive error port 0

MII_TX_ENA0

OUTPUT

Transmit enable port 0

MII_TX_DATA0[3:0]

OUTPUT

Transmit data port 0

Port0 = MII and TX

Shift activated

MII_TX_CLK0

INPUT

Transmit clock port 0 for

automatic TX Shift

configuration. Set to 0 for

manual TX Shift

configuration.

MII_TX_SHIFT0[1:0]

INPUT

Manual TX shift

configuration port 0.

Additional TX signal delay:

00: 0 ns

01: 10 ns

10: 20 ns

11: 30 ns

Port1 = MII

nMII_LINK1

INPUT

0: 100 Mbit/s (Full

Duplex) link at port 1

1: no link at port 1

MII_RX_CLK1

INPUT

Receive clock port 1

MII_RX_DV1

INPUT

Receive data valid port 1

MII_RX_DATA1[3:0]

INPUT

Receive data port 1

MII_RX_ERR1

INPUT

Receive error port 1

MII_TX_ENA1

OUTPUT

Transmit enable port 1

MII_TX_DATA1[3:0]

OUTPUT

Transmit data port 1

Port1 = MII and TX

Shift activated

MII_TX_CLK1

INPUT

Transmit clock port 1 for

automatic TX Shift

configuration. Set to 0 for

manual TX Shift

configuration.

MII_TX_SHIFT1[1:0]

INPUT

Manual TX shift

configuration port 1.

Additional TX signal delay:

00: 0 ns

01: 10 ns

10: 20 ns

11: 30 ns