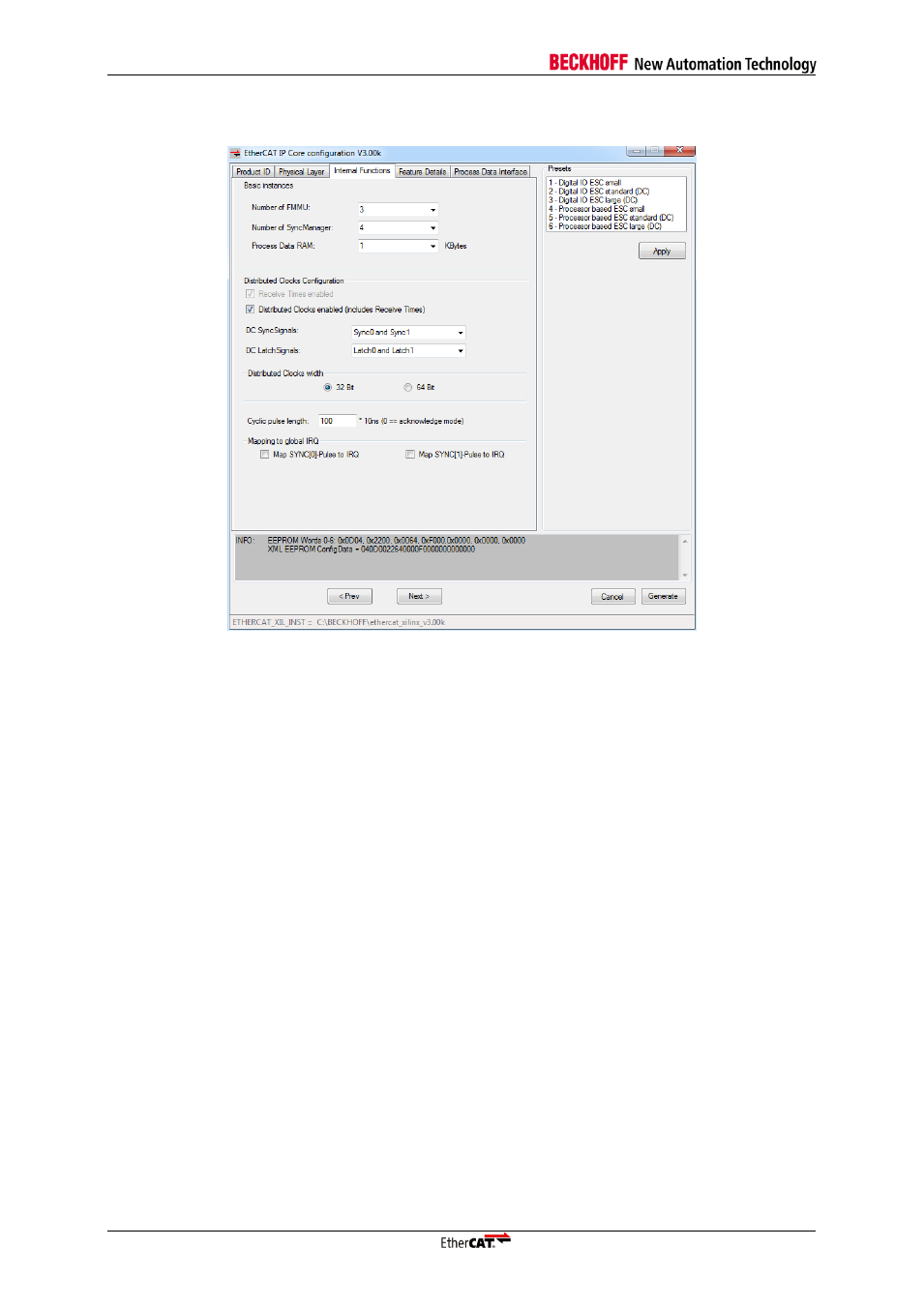

3 internal functions tab, Internal functions tab, Figure 15: internal functions tab – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 50

IP Core Configuration

III-38

Slave Controller

– IP Core for Xilinx FPGAs

5.1.3

Internal Functions tab

Figure 15: Internal Functions tab

FMMUs

Number of FMMU instances. Between 0 and 8 FMMUs are possible.

SyncManager

Number of SyncManager instances. Between 0 and 8 SyncManagers are possible.

Process Data RAM

The size of the Process data memory can be determined in this dialog. Minimum memory size is

0 KByte, maximum memory size is 60 KByte.

Receive Times enabled

The Distributed Clocks receive time feature for propagation delay calculation can be enabled without

using all DC features. They will be automatically enabled for configurations with 3 ports.

Distributed Clocks enabled

The Distributed Clocks feature comprises synchronized distributed clocks, receive times, SyncSignal

generation, and LatchSignal time stamping.

DC SyncSignals

Select the number of SyncSignals.

DC LatchSignals

Select the number of LatchSignals.

Distributed Clocks Width

The width of the Distributed Clocks can be selected to be either 32 bit or 64 bit. DC with 64 bit require

more FPGA resources. DC with 32 bit and DC with 64 bit are interoperable.

Cyclic pulse length

Determines the length of SyncSignal output (register 0x0982:0x0983).