3 spi slave interface, 4 asynchronous 8/16 bit µcontroller interface, Spi slave interface – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 83: Asynchronous 8/16 bit µcontroller interface, Table 28: spi pdi, Table 29: 8/16 bit µc pdi

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-71

8.6.3

SPI Slave Interface

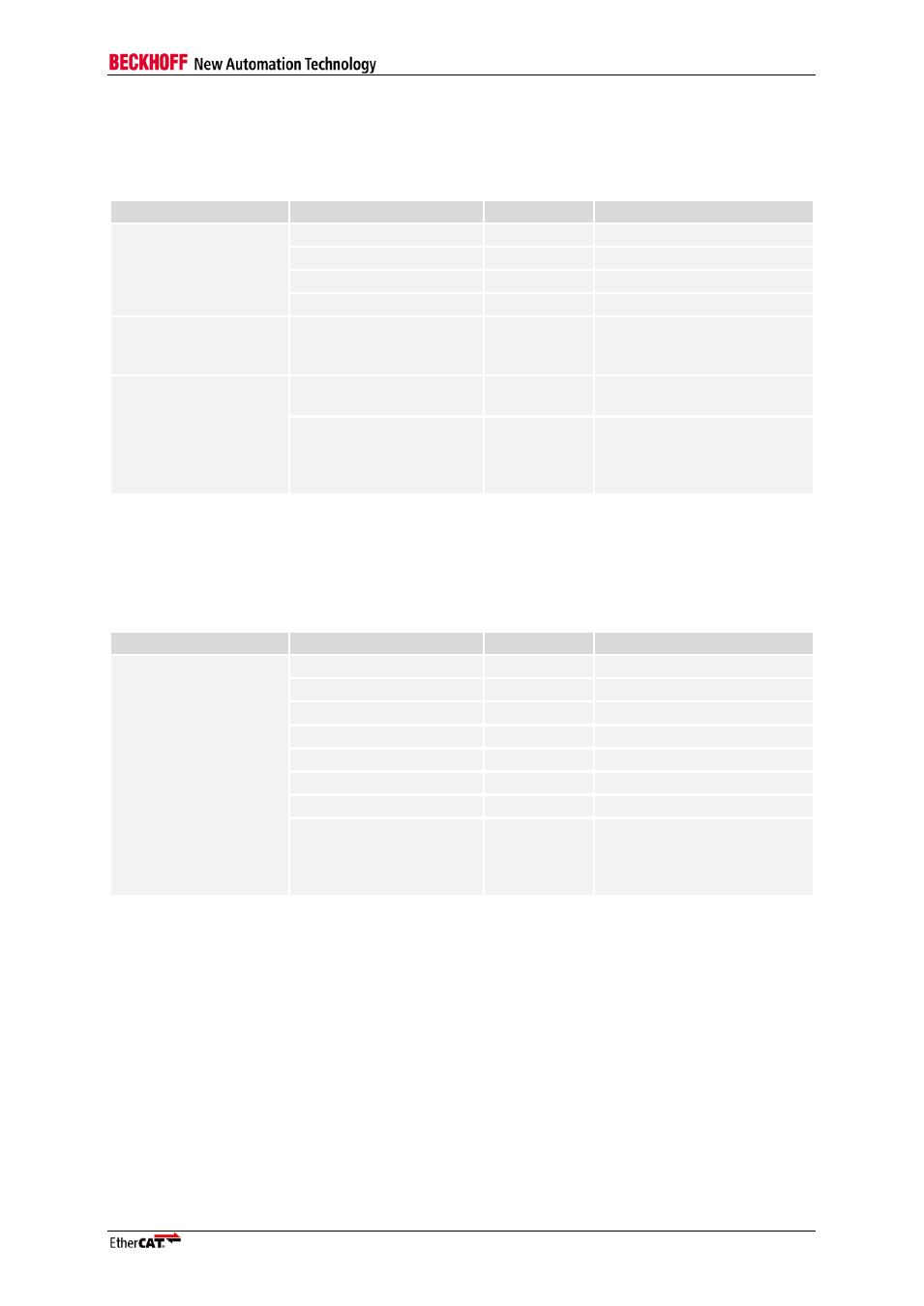

Table 28 used with an SPI PDI.

Table 28: SPI PDI

Condition

Name

Direction

Description

SPI PDI

PDI_SPI_CLK

INPUT

SPI clock

PDI_SPI_SEL

INPUT

SPI slave select

PDI_SPI_DI

INPUT

SPI slave data in (MOSI)

PDI_SPI_IRQ

OUTPUT

SPI interrupt

Tristate drivers inside

core (SPI

configuration)

PDI_SPI_DO

OUTPUT

SPI slave data out (MISO)

External tristate drivers

PDI_SPI_DO_OUT

OUTPUT

SPI slave data out:

IP Core µC

PDI_SPI_DO_ENA

OUTPUT

0: disable output driver for

PDI_SPI_DO_OUT

1: enable output driver for

PDI_SPI_DO_OUT

8.6.4

Asynchronous 8/16 Bit µController Interface

Table 29 lists the signals used with both, 8 Bit and 16 Bit asynchronous µController PDI.

Table 29: 8/16 Bit µC PDI

Condition

Name

Direction

Description

8/16 Bit µC

PDI_uC_ADR[15:0]

INPUT

µC address bus

PDI_uC_nBHE

INPUT

µC byte high enable

PDI_uC_nRD

INPUT

µC read access

PDI_uC_nWR

INPUT

µC write access

PDI_uC_nCS

INPUT

µC chip select

PDI_uC_IRQ

OUTPUT

Interrupt

PDI_uC_BUSY

OUTPUT

PDI busy

PDI_uC_DATA_ENA

OUTPUT

0: disable output driver for

PDI_uC_DATA_OUT

1: enable output driver for

PDI_uC_DATA_OUT