1 major differences between v2.04x and v3.00x, 2 reading ip core version from device, Major differences between v2.04x and v3.00x – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 21: Reading ip core version from device, Table 5: register revision (0x0001), Table 6: register build (0x0002:0x0003)

Overview

Slave Controller

– IP Core for Xilinx FPGAs

III-9

1.7.1

Major differences between V2.04x and V3.00x

The EtherCAT IP Core V3.00x versions have these advantages compared with the V2.04x versions:

Increased PDI performance (average latency internally at least by a factor of 2 faster; worst case

latency even better)

Support for 8/16/32/64 bit AXI4

TM

and AXI4 LITE

TM

interface

Support for RGMII ports

Native support for FX PHYs

Flexible PHY address configuration

Support for PDI SyncManager/IRQ acknowledge by Write command (required for wide on-chip-

busses)

More detailed configuration

The higher PDI performance increases the resource requirements of the V3.00x versions compared

with the V2.04x versions. New development is focused on the V3.00x versions.

1.7.2

Reading IP Core version from device

The IP Core version, denoted as X.Yz (e.g., 1.00a), consists of three values X, Y, and z. These values

can be read out in registers 0x0001 and 0x0002. Value z is encoded like this: a=0, b=1, c=2, etc. .

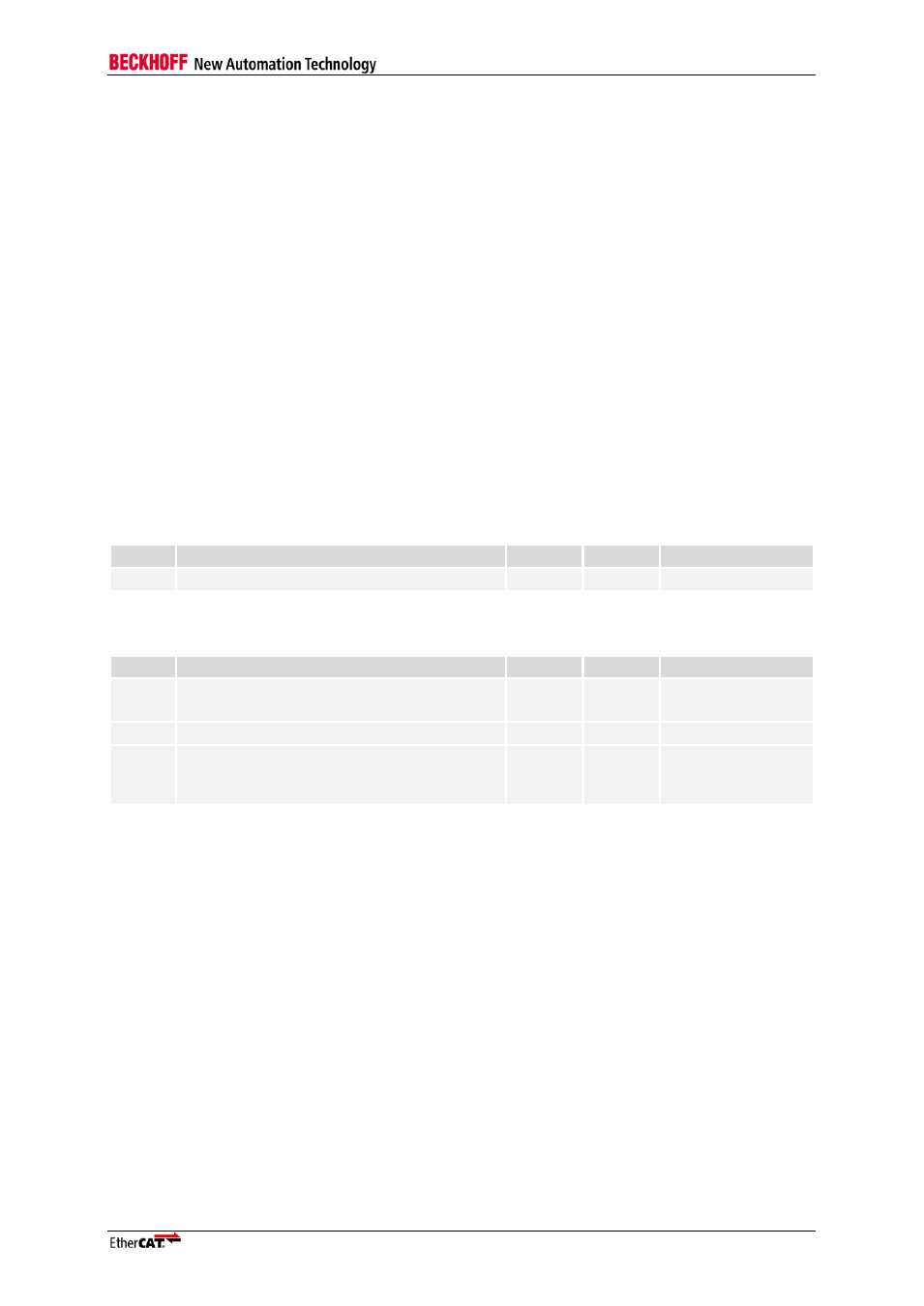

Table 5: Register Revision (0x0001)

Bit

Description

ECAT

PDI

Reset Value

7:0

IP Core major version X

r/-

r/-

IP Core dep.

Table 6: Register Build (0x0002:0x0003)

Bit

Description

ECAT

PDI

Reset Value

3:0

IP Core maintenance version z

r/-

r/-

IP Core dep.

7:4

IP Core minor version Y

r/-

r/-

IP Core dep.

15:8

Patch level:

0x00:

original release

0x01-0x0F:

patch level of original release

r/-

r/-

IP Core dep.