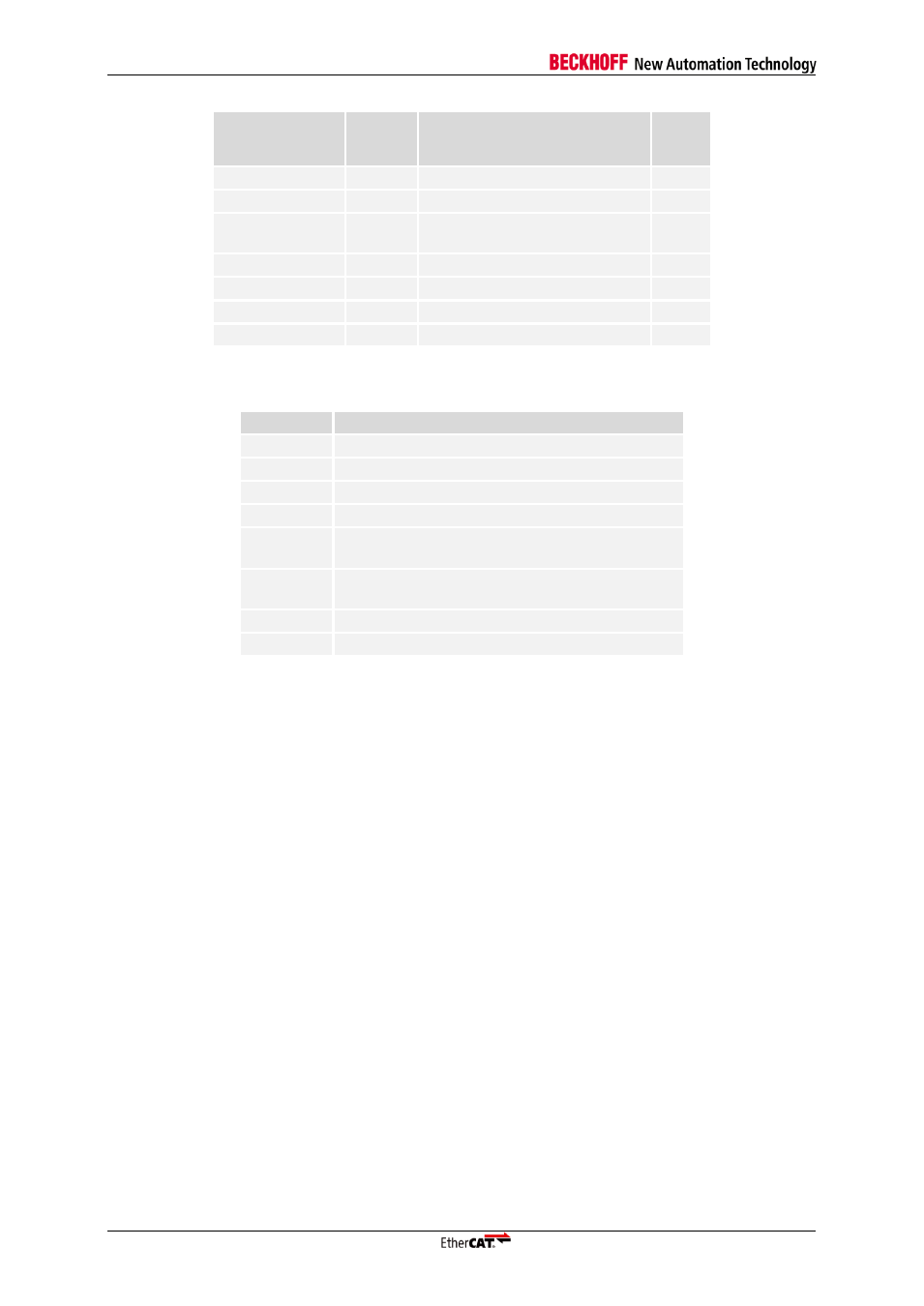

Table 10: legend – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 30

Features and Registers

III-18

Slave Controller

– IP Core for Xilinx FPGAs

Address

Length

(Byte)

Description

IP Core

V3.00c-

V3.00k

0x0E08:0x0E0F

8

Vendor ID

x

0x0F00:0x0F03

4

Digital I/O Output Data

io

0x0F10:0x0F17

8

General Purpose Outputs

[Byte]

0-8

0x0F18:0x0F1F

8

General Purpose Inputs [Byte]

0-8

0x0F80:0x0FFF

128

User RAM

x

0x1000:0x1003

4

Digital I/O Input Data

io

0x1000 ff.

Process Data RAM [Kbyte]

1-60

Table 10: Legend

Symbol

Description

x

Available

-

Not available

r

Read only

c

Configurable

dc

Available if Distributed Clocks with all

Sync/Latch signals are enabled

rt

Available if Receive Times or Distributed Clocks

are enabled (always available for 3-4 ports)

io

Available if Digital I/O PDI is selected

red

Register changed in this version