BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 34

Advertising

Features and Registers

III-22

Slave Controller

– IP Core for Xilinx FPGAs

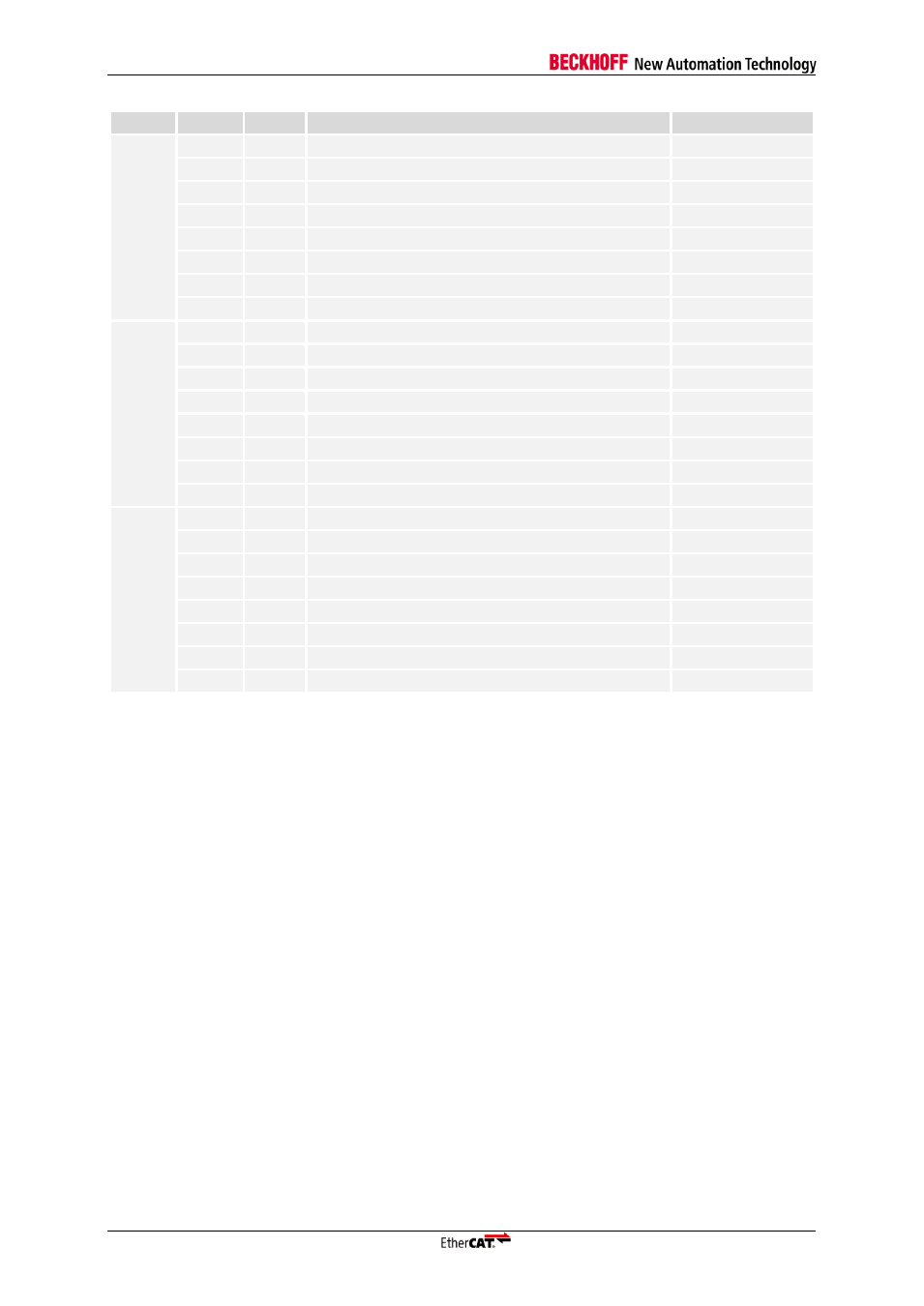

Addr.

Bit

Feat.

Description

Reset Value

0F91

0

128

Reserved

0

1

129

Reserved

0

2

130

Reserved

0

3

131

Reserved

0

4

132

Reserved

0

5

133

Reserved

0

6

134

Reserved

0

7

135

Reserved

0

0F92

0

136

Reserved

0

1

137

Reserved

0

2

138

Reserved

0

3

139

Reserved

0

4

140

Reserved

0

5

141

Reserved

0

6

142

Reserved

0

7

143

Reserved

0

0F93

0

144

RGMII

c

1

145

Individual PHY address read out (0x0510[7:3])

c

2

146

CLK_PDI_EXT is asynchronous

c

3

147

Reserved

0

4

148

Use RGMII GTX_CLK phase shifted clock input

1

5

149

RMII

c

6

150

Reserved

0

7

151

Reserved

0

Advertising