1 frame processing order, Frame processing order, Table 2: frame processing order – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 14: Figure 2: frame processing, Ethercat ip core

Overview

III-2

Slave Controller

– IP Core for Xilinx FPGAs

1.1

Frame processing order

The frame processing order of the EtherCAT IP Core is as follows (logical port numbers are used):

Table 2: Frame Processing Order

Number of Ports

Frame processing order

1

0

→EtherCAT Processing Unit→0

2

0

→EtherCAT Processing Unit→1 / 1→0

3

0

→EtherCAT Processing Unit→1 / 1→2 / 2→0 (log. ports 0,1, and 2)

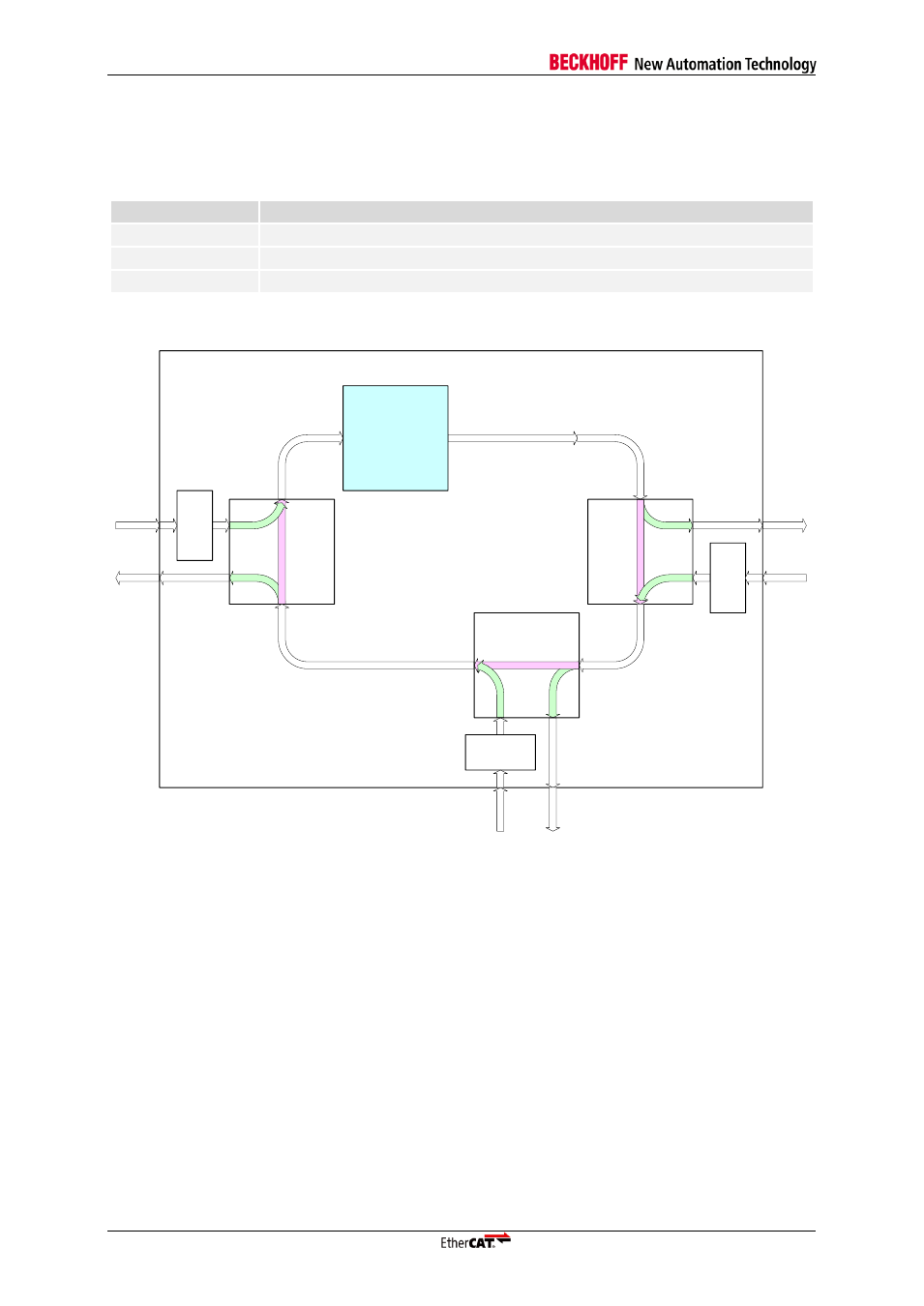

Figure 2 shows the frame processing in general:

1

Port 1

A

u

to

-

F

o

rw

a

rd

e

r

Port 0

A

u

to

-

F

o

rw

a

rd

e

r

L

o

o

p

b

a

c

k

f

u

n

c

ti

o

n

EtherCAT

Processing Unit

L

o

o

p

b

a

c

k

f

u

n

c

ti

o

n

EtherCAT IP Core

p

o

rt

1

c

lo

s

e

d

p

o

rt

1

o

p

e

n

p

o

rt

0

o

p

e

n

o

r

a

ll

p

o

rt

s

c

lo

s

e

d

p

o

rt

0

c

lo

s

e

d

Port 2

Auto-

Forwarder

Loopback function

port 2 closed

port 2 open

Figure 2: Frame Processing

Frame Processing Example with Ports 0 and 1

A frame received at port 0 goes via the Auto-Forwarder and the Loopback function to the EtherCAT

Processing Unit which processes it. Then, the frame is sent to port 1. If port 1 is open, the frame is

sent out at port 1. If it is closed, the frame is forwarded by the Loopback function to port 2. Since port 2

is not configured, the Loopback function of port 2 forwards the frame to the Loopback function of port

0, and then it is sent out at port 0

– back to the master.