BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 33

Features and Registers

Slave Controller

– IP Core for Xilinx FPGAs

III-21

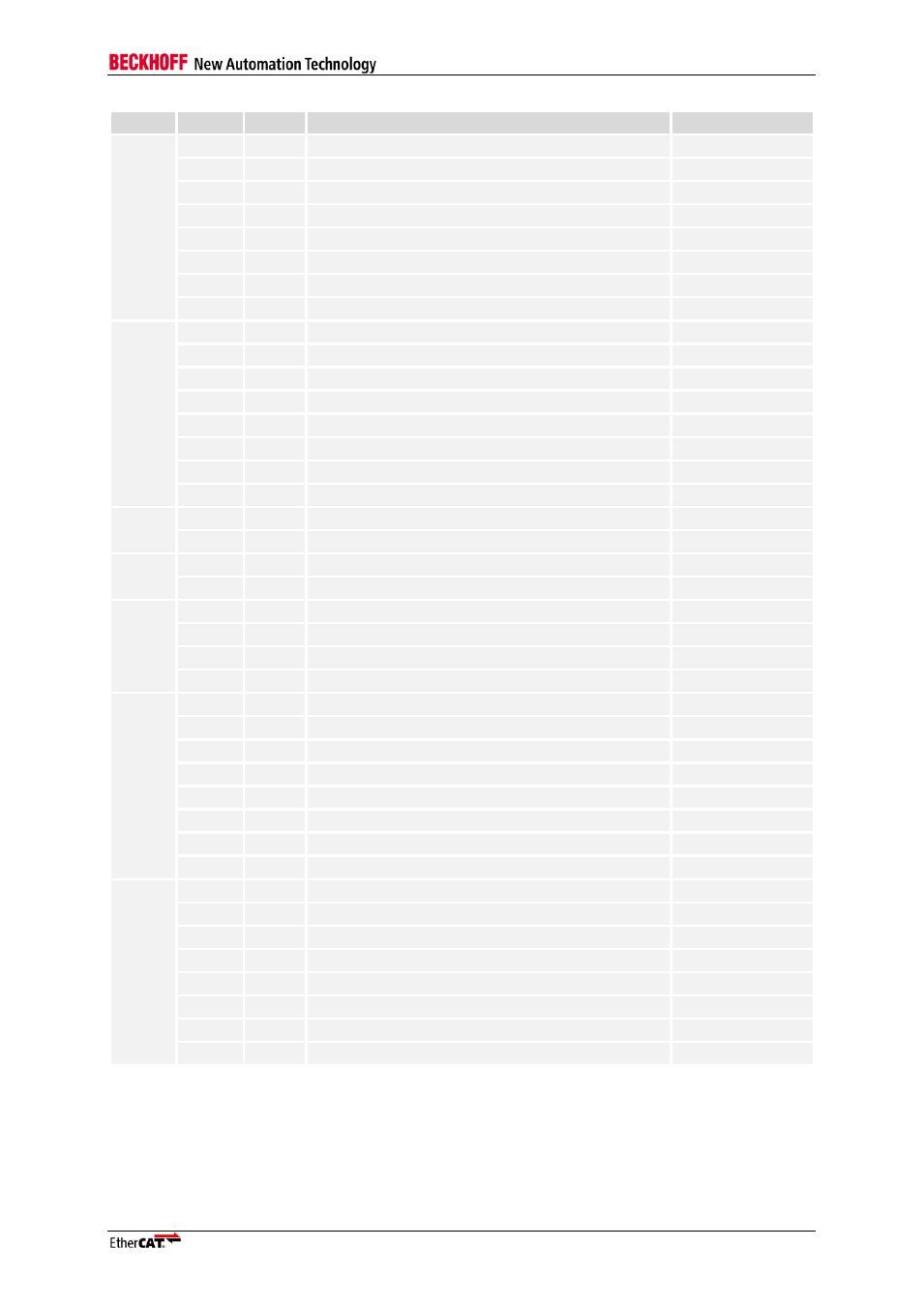

Addr.

Bit

Feat.

Description

Reset Value

0F8A

0

72

Reserved

0

1

73

Reserved

1

2

74

DC Latch1 disable

c

3

75

AXI PDI

c

4

76

Reserved

0

5

77

Reserved

0

6

78

PDI function acknowledge by PDI write

c

7

79

Reserved

0

0F8B

0

80

Reserved

1

1

81

Reserved

1

2

82

Reserved

0

3

83

LED test

c

4

84

Reserved

0

5

85

Reserved

0

6

86

Reserved

0

7

87

Reserved

0

0F8C

3:0

91:88

Reserved

0

7:4

95:92

Reserved

0

0F8D

3:0

99:96

Reserved

0

7:4

103:100

Reserved

0

0F8E

3:0

107:104

Reserved

0

4

108

Reserved

0

5

109

Reserved

0

7:6

111:110

Digital I/O PDI byte size

c

0F8F

0

112

Reserved

0

1

113

Reserved

0

2

114

Digital I/O PDI

c

3

115

SPI PDI

c

4

116

Asynchronous µC PDI

c

5

117

Reserved

0

6

118

Reserved

1

7

119

Reserved

1

0F90

0

120

Reserved

0

1

121

Reserved

0

2

122

Reserved

0

3

123

Reserved

0

4

124

Reserved

0

5

125

Reserved

0

6

126

Reserved

0

7

127

Reserved

0