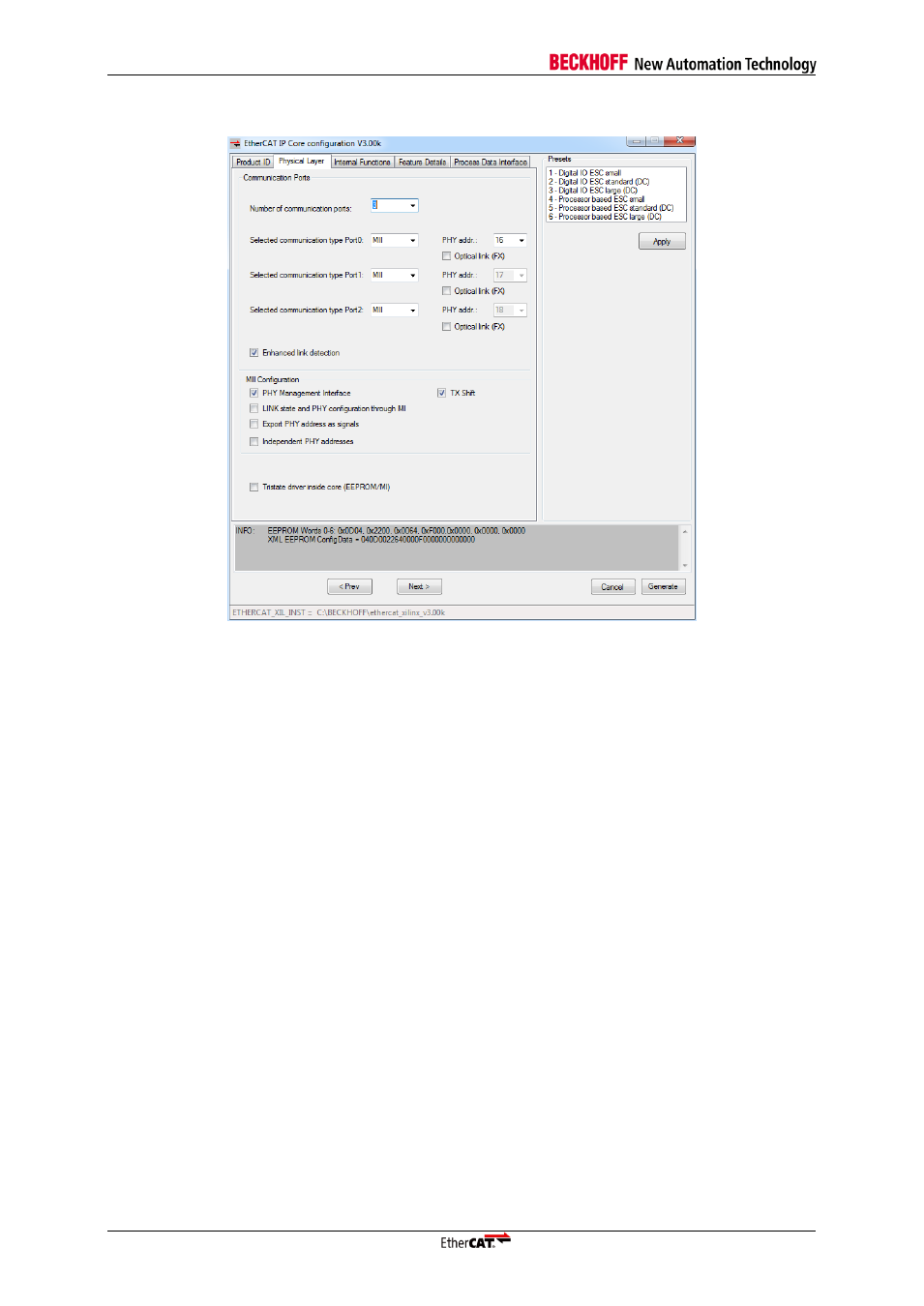

2 physical layer tab, Physical layer tab, Figure 14: physical layer tab – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 48

IP Core Configuration

III-36

Slave Controller

– IP Core for Xilinx FPGAs

5.1.2

Physical Layer tab

Figure 14: Physical Layer tab

Communication Ports

The number of communication ports by default is two. As PHY interface MII/RGMII (1, 2, or 3 ports) or

RMII (1 or 2 ports only) can be selected. It is recommended to use MII as for accuracy of the

distributed clocks is much better with MII.

Optical link (FX)

Each port can be configured to be an FX (fiber optic) port which has influence on Enhanced Link

Detection and MI link detection and configuration, since FX connections do not use Auto-negotiation.

Enhanced link detection

Enhanced MII link detection is a mechanism of informing link partners of receive errors.

TX Shift

Automatic or manual TX Shift is available if TX Shift is selected. TX Shift delays MII TX signals to

comply to Ethernet PHY setup and hold timing. Automatic TX Shift uses the TX_CLK signals of the

PHYs to detect appropriate TX Shift settings automatically. Manual TX Shift configuration allows for

delaying the MII TX signals by 0, 10, 20, or 30 ns.

PHY Management Interface

The PHY Management Interface function can be selected or deselected. If it deselected, the other MII

Configuration options are not available.

LINK state and PHY configuration through MI

MI link detection and configuration is available if checked. Ethernet PHYs are configured and link

status is polled via the MII Management Interface. Enhanced link detection has to be activated if MI

link detection and configuration is used and the nMII_LINK0/1/2 signals are not used.

Export PHY address as signals

Enable for dynamically changing PHY addresses (the PHY address configuration is exported as

signals), otherwise the PHY address configuration is static.