BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 70

FPGA Resource Consumption

III-58

Slave Controller

– IP Core for Xilinx FPGAs

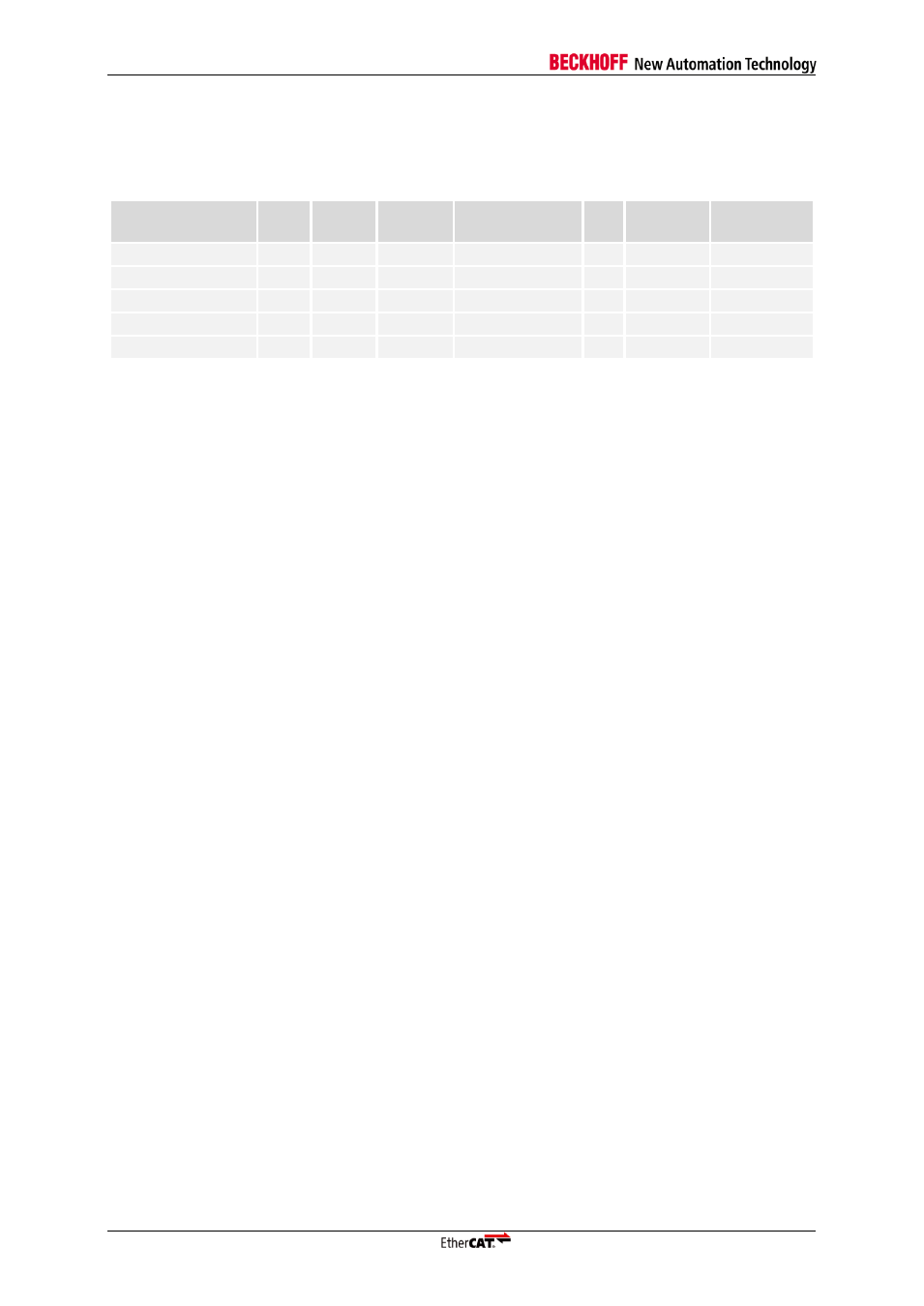

The EtherCAT IP core resource consumption figures for typical EtherCAT devices are based on

EtherCAT IP Core for Xilinx FPGAs Version 3.00c, Xilinx ISE 14.5, and Spartan-6 devices.

Table 17: EtherCAT IP Core resource consumption for typical EtherCAT Devices

EtherCAT Device

SM

FMMU

DPRAM

[kByte]

PDI

DC

Reg.

LUT6

IO

2

2

1

32 Bit Digital I/O

-

4,800

5,800

Frequency Inverter

4

4

1

SPI

-

7,000

10,000

Encoder

4

4

1

SPI

32

9,900

13,200

Fieldbus Gateway

4

4

4

16 Bit µC

-

6,600

9,900

Servo Drive

4

4

4

16 Bit µC

32

9,400

13,200

NOTE: Register preset is standard. All devices have 2 MII ports including MII Management Interface, DC is 32 bit

wide (2 SyncSignals, 2 LatchSignals).