7 sof, 8 outvalid, 9 timing specifications – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 107: Outvalid, Timing specifications

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-95

10.1.7 SOF

SOF indicates the start of an Ethernet/EtherCAT frame. It is asserted shortly after RX_DV=1 or EBUS

SOF. Input data is sampled in the time interval between t

SOF_to_DATA_setup

and t

SOF_to_DATA_setup

after the

SOF signal is asserted.

10.1.8 OUTVALID

A pulse on the OUTVALID signal indicates an output event. If the output event is configured to be the

end of a frame, OUTVALID is issued shortly after RX_DV=0 or EBUS EOF, right after the CRC has

been checked and the internal registers have taken their new values. OUTVALID is issued

independent of actual output data values, i.e., it is issued even if the output data does not change.

10.1.9 Timing specifications

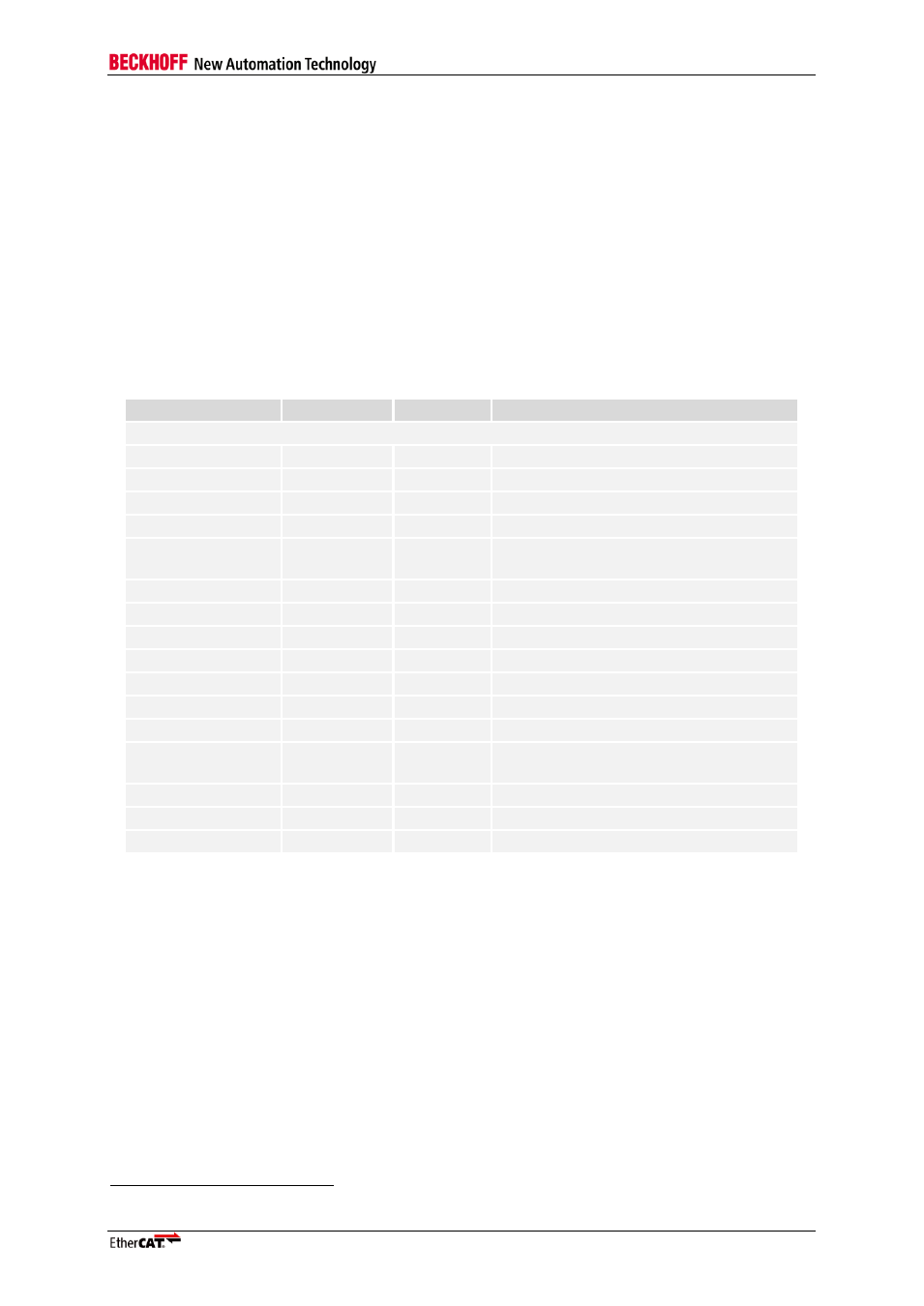

Table 46: Digital I/O timing characteristics IP Core

Parameter

Min

Max

Comment

PRELIMINARY TIMING

t

DATA_setup

x

5

Input data valid before LATCH_IN

t

DATA_hold

Input data valid after LATCH_IN

t

LATCH_IN

LATCH_IN high time

t

SOF

40 ns

– x

40 ns + x

SOF high time

t

SOF_to_DATA_setup

0 ns

1,2 µs - x

Input data valid after SOF, so that Inputs

can be read in the same frame

t

SOF_to_DATA_hold

1,6 µs + x

Input data invalid after SOF

t

input_event_delay

440 ns

Time between consecutive input events

t

OUTVALID

80 ns

– x

80 ns + x

OUTVALID high time

t

DATA_to_OUTVALID

80 ns

– x

Output data valid before OUTVALID

t

WD_TRIG

40 ns

– x

40 ns + x

WD_TRIG high time

t

DATA_to_WD_TRIG

20 ns + x

Output data valid after WD_TRIG

t

DATA_to_SYNC

10 ns + x

Output data valid after SYNC0/1

t

OE_EXT_to_DATA_invalid

0 ns

Outputs zero or Outputs high impedance

after OE_EXT set to low

t

output_event_delay

320 ns

Time between consecutive output events

t

OUT_ENA_valid

80 ns

– x

OUT_ENA valid before OUTVALID

t

OUT_ENA_invalid

80 ns

– x

OUT_ENA invalid after OUTVALID

5

EtherCAT IP Core: time depends on synthesis results