9 timing specification, Timing specification – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 125

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-113

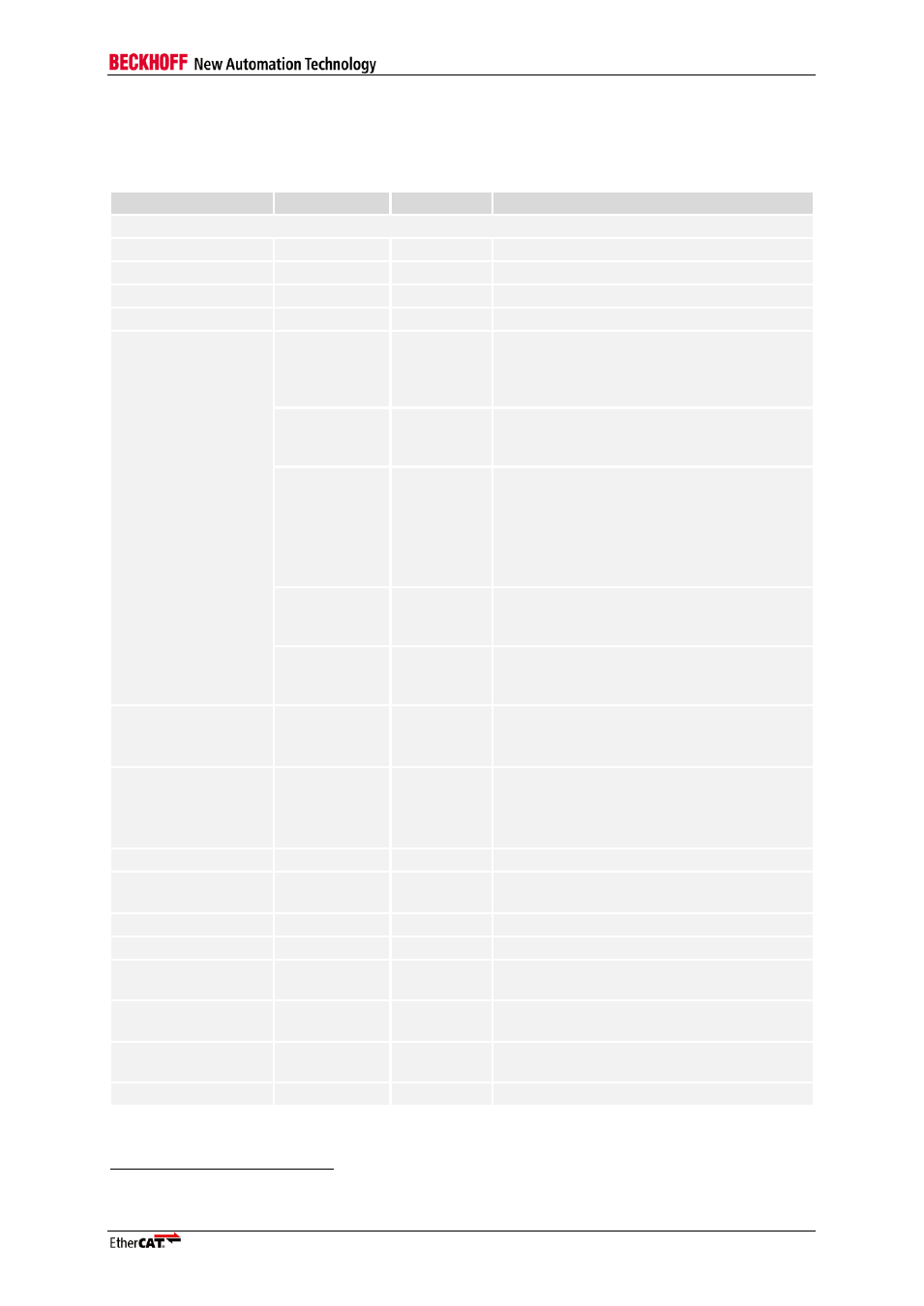

10.3.9 Timing Specification

Table 57: µController timing characteristics IP Core

Parameter

Min

Max

Comment

PRELIMINARY TIMING

t

CS_to_BUSY

x

10

BUSY driven and valid after CS assertion

t

ADR_BHE_setup

ADR and BHE valid before RD assertion

t

RD_to_DATA_driven

0 ns

11

DATA bus driven after RD assertion

t

RD_to_BUSY

BUSY asserted after RD assertion

t

read

External read time (RD assertion to BUSY

deassertion) with normal read busy output

(0x0152[0]). Additional 20 ns if delayed read

busy output is configured.

a) t

read_int

a) without preceding write access or

t

WR_to_RD

≥

t

write_int

or configuration: write after

falling edge of WR

b) t

read_int

+ t

write_int

-t

b) with preceding write access and

t

WR_to_RD

< t

write_int

c) 245 ns

c) 8 bit access, absolute worst case with

preceding write access (t

WR_to_RD

=min

,

t

write_int

=max)

d) 285 ns

d) 16 bit access, absolute worst case with

preceding write access (t

WR_to_RD

=min

,

t

write_int

=max)

t

read_int

a) 110 ns

b) 150 ns

a) 150 ns

b) 190 ns

Internal read time

a) 8 bit access

b) 16 bit access

t

BUSY_to_DATA_valid

-5 ns

-20 ns

DATA bus valid after device BUSY is

deasserted

a) normal read busy output

b) delayed read busy output

t

ADR_BHE_to_DATA_invalid

DATA invalid after ADR or BHE change

t

CS_RD_to_DATA_release

DATA bus released after CS deassertion or

RD deassertion

t

CS_to_BUSY_release

BUSY released after CS deassertion

t

CS_delay

Delay between CS deassertion an assertion

t

RD_delay

Delay between RD deassertion and

assertion

t

ADR_BHE_DATA_setup

ADR, BHE and Write DATA valid before WR

deassertion

t

ADR_BHE_DATA_hold

ADR, BHE and Write DATA valid after WR

deassertion

t

WR_active

WR assertion time

10

EtherCAT IP Core: time depends on synthesis results

11

EtherCAT IP Core: time depends on synthesis results, specified value has to be met anyway