3 timing specifications, Timing specifications, Table 60: plb timing characteristics – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 131

Advertising

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-119

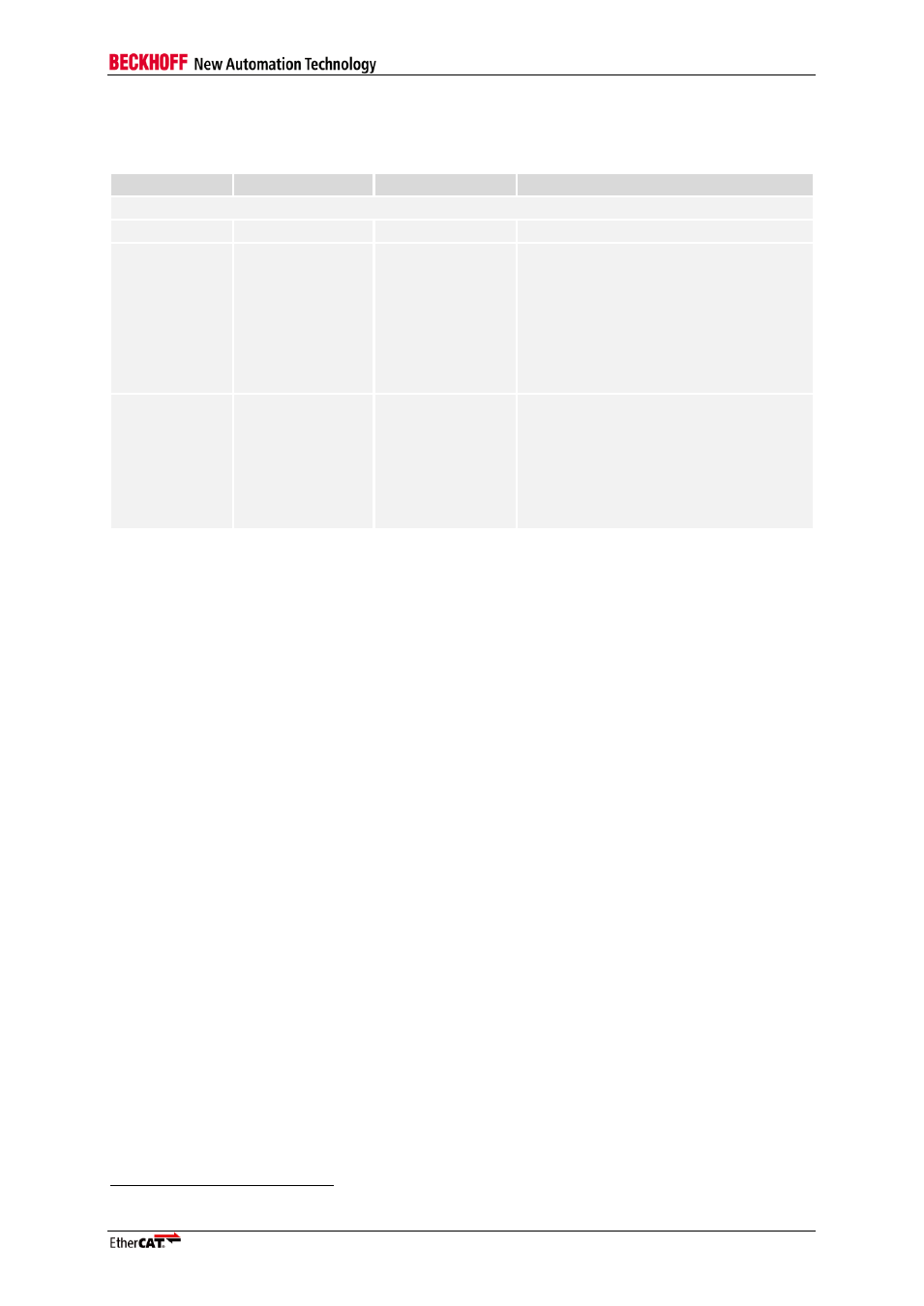

10.4.3 Timing specifications

Table 60: PLB timing characteristics

Parameter

Min

Max

Comment

PRELIMINARY TIMING

t

Clk

x

13

40 ns

PLB bus clock (f

Clk

≥25 MHz)

t

Read

a) 4* t

CLK

+160 ns

+x

b) 6.5 * t

CLK

+260 ns

+x

a) 3* t

CLK

+200 ns

+x

b) 5.5 * t

CLK

+300 ns

+x

32 Bit read access time

a) synchronous (N=1-31)

b) asynchronous

t

Write

a) 4* t

CLK

b) 6.5 * t

CLK

+100 ns

+x

a) 200 ns

+x

b) 2.5 * t

CLK

+300 ns

+x

32 Bit write access time

a) synchronous (N=1-31)

b) asynchronous

13

EtherCAT IP Core: time depends on synthesis results

Advertising