11 distributed clocks sync/latch signals, 1 signals, 2 timing specifications – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 138: Distributed clocks sync/latch signals, Signals, Timing specifications, Table 64: distributed clocks signals, Figure 63: distributed clocks signals, Figure 64: latchsignal timing, Figure 65: syncsignal timing

Distributed Clocks SYNC/LATCH Signals

III-126

Slave Controller

– IP Core for Xilinx FPGAs

11 Distributed Clocks SYNC/LATCH Signals

For details about the Distributed Clocks refer to Section I.

11.1 Signals

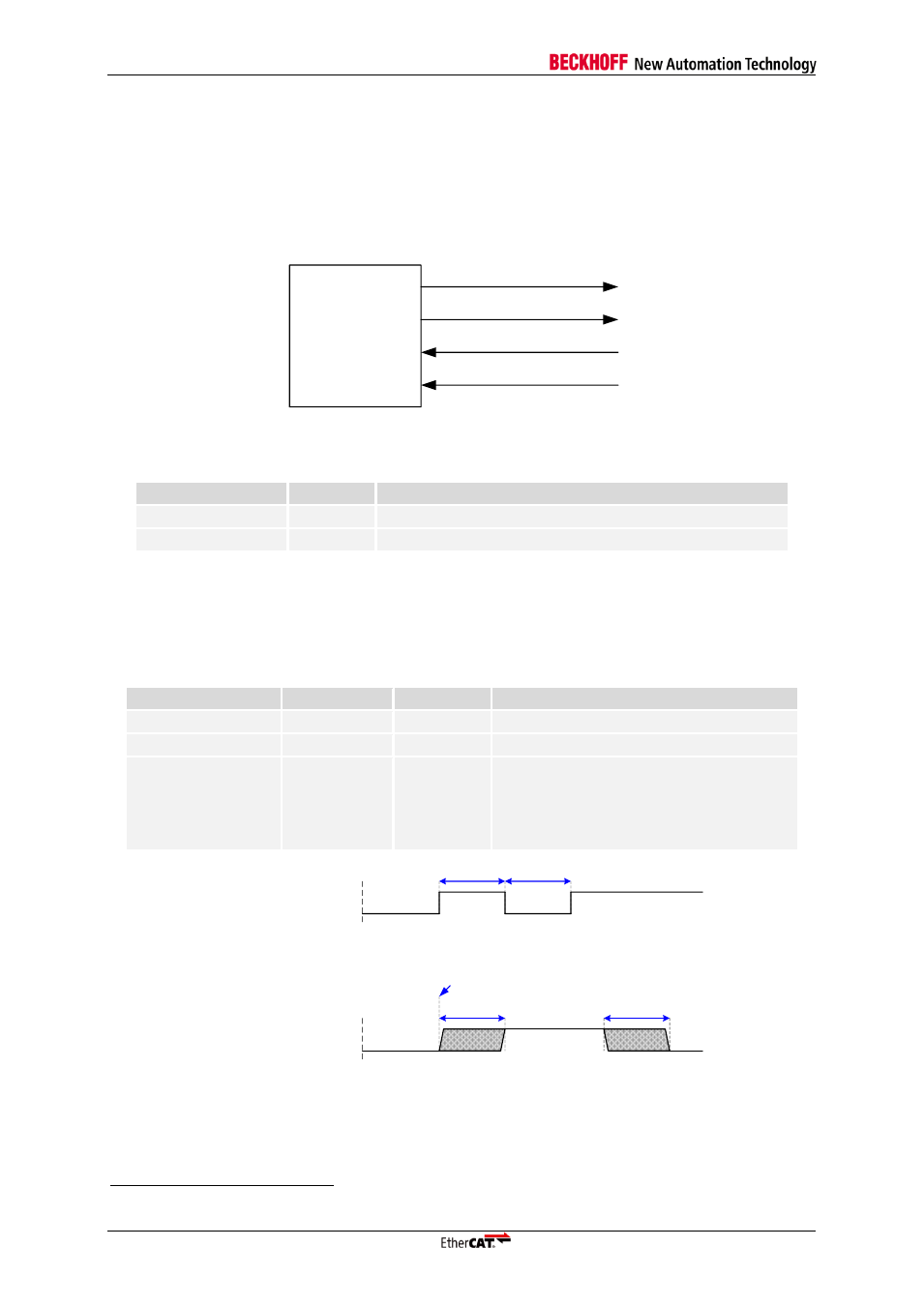

The Distributed Clocks unit of the IP Core has the following external signals (depending on the ESC

configuration):

EtherCAT

device

LATCH_IN0

SYNC_OUT1

SYNC_OUT0

LATCH_IN1

Figure 63: Distributed Clocks signals

Table 64: Distributed Clocks signals

Signal

Direction

Description

SYNC_OUT0/1

OUT

SyncSignals (alias SYNC[1:0])

LATCH_IN0/1

IN

LatchSignals (alias LATCH[1:0])

NOTE: SYNC_OUT0/1 are active high/push-pull outputs.

11.2 Timing specifications

Table 65: DC SYNC/LATCH timing characteristics IP Core

Parameter

Min

Max

Comment

t

DC_LATCH

12 ns + x

16

Time between Latch0/1 events

t

DC_SYNC_Jitter

11 ns + x

SYNC0/1 output jitter

t

DC_SYNC_IRQ_pulse_width

40 ns

SYNC0/1 pulse width if the SYNC0/1

signal is used as AL event request (PDI

interrupt) signal (masked by register

0x0220 ff.), and if acknowledge mode is

not used.

LATCH0/1

t

DC_LATCH

t

DC_LATCH

Figure 64: LatchSignal timing

SYNC0/1

t

DC_SYNC_Jitter

Output event time

t

DC_SYNC_Jitter

Figure 65: SyncSignal timing

16

EtherCAT IP Core: time depends on synthesis results