3 extended esc features in user ram, Extended esc features in user ram, 0x0f80:0x0fff) – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 31

Features and Registers

Slave Controller

– IP Core for Xilinx FPGAs

III-19

2.3

Extended ESC Features in User RAM

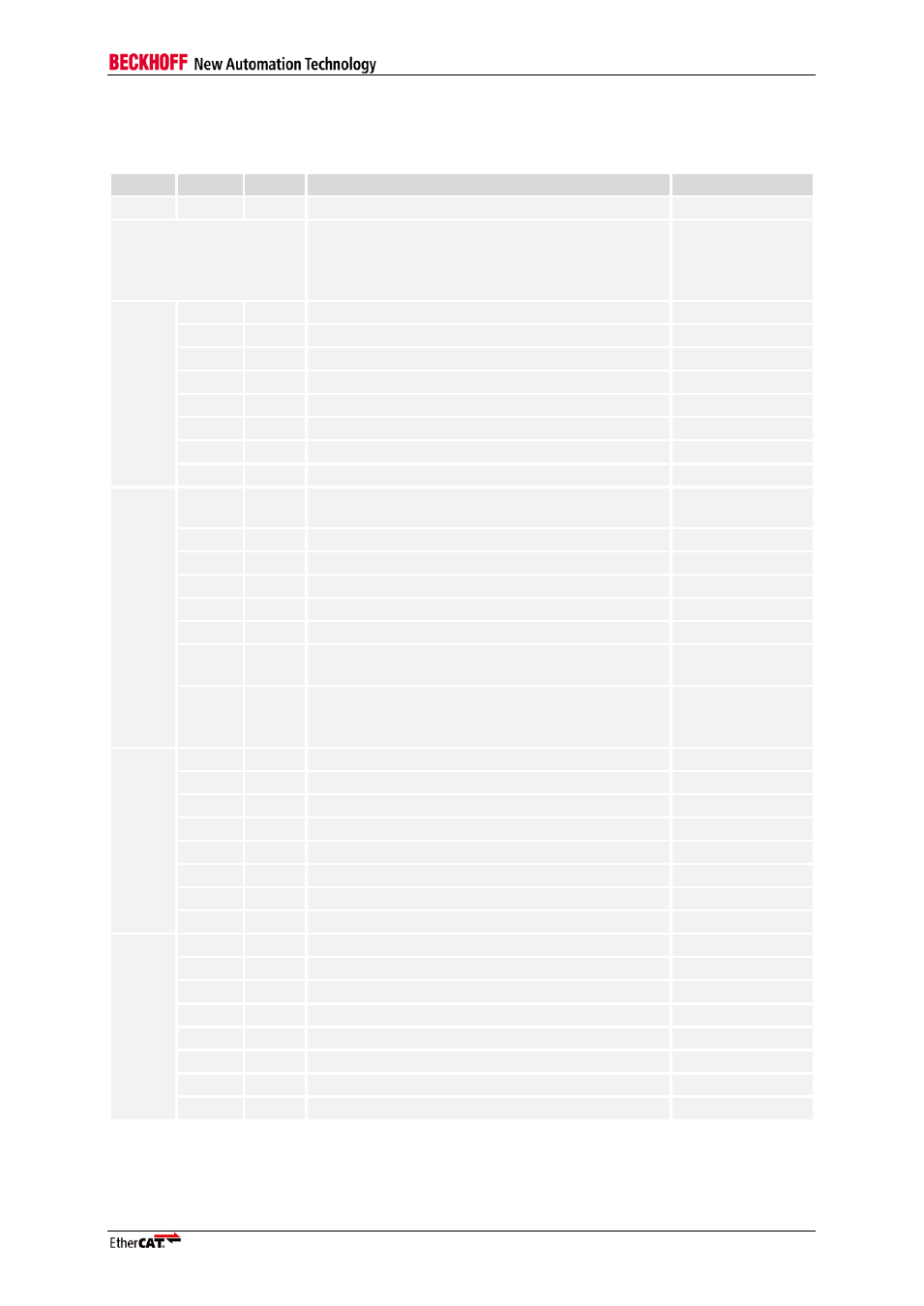

Table 11: Extended ESC Features (Reset values of User RAM

– 0x0F80:0x0FFF)

Addr.

Bit

Feat.

Description

Reset Value

0F80

7:0

-

Number of extended feature bits

Depends on ESC

IP Core extended features:

Depends on ESC:

0:

Not available

1:

Available

c:

Configurable

0F81

0

0

Extended DL Control Register (0x0102:0x0103)

1

1

1

AL Status Code Register (0x0134:0x0135)

c

2

2

ECAT Interrupt Mask (0x0200:0x0201)

1

3

3

Configured Station Alias (0x0012:0x0013)

1

4

4

General Purpose Inputs (0x0F18:0x0F1F)

c

5

5

General Purpose Outputs (0x0F10:0x0F17)

c

6

6

AL Event Mask (0x0204:0x0207)

c

7

7

Physical Read/Write Offset (0x0108:0x0109)

c

0F82

0

8

Watchdog divider writeable (0x0400:0x04001) and

Watchdog PDI (0x0410:0x0f11)

c

1

9

Watchdog counters (0x0442:0x0443)

c

2

10

Write Protection (0x0020:0x0031)

c

3

11

Reset (0x0040:0x0041)

c

4

12

Reserved

0

5

13

DC SyncManager Event Times (0x09F0:0x09FF)

c

6

14

ECAT Processing Unit/PDI Error Counter

(0x030C:0x030D)

c

7

15

EEPROM Size configurable (0x0502.7):

0:

EEPROM Size fixed to sizes up to 16 Kbit

1:

EEPROM Size configurable

1

0F83

0

16

Reserved

1

1

17

Reserved

0

2

18

Reserved

0

3

19

Lost Link Counter (0x0310:0x0313)

c

4

20

MII Management Interface (0x0510:0x0515)

c

5

21

Enhanced Link Detection MII

c

6

22

Enhanced Link Detection EBUS

0

7

23

Run LED (DEV_STATE LED)

c

0F84

0

24

Link/Activity LED

1

1

25

Reserved

0

2

26

Reserved

1

3

27

DC Latch In Unit

c

4

28

Reserved

0

5

29

DC Sync Out Unit

c

6

30

DC Time loop control assigned to PDI

c

7

31

Link detection and configuration by MI

c